# DEVICE ENGINEERING INCORPORATED

385 East Alamo Drive Chandler, AZ 85225 Phone: (480) 303-0822 Fax: (480) 303-0824 E-mail: admin@deiaz.com

# DEI1026 Six Channel Discrete-to-Digital Interface Sensing Open/Ground Signals

### Features:

- Senses six Open/Ground Inputs

- Inputs are lightning protected to DO-160D Level 3

- TTL/CMOS-Compatible Tri-State Outputs

- Package / Temperature Options:

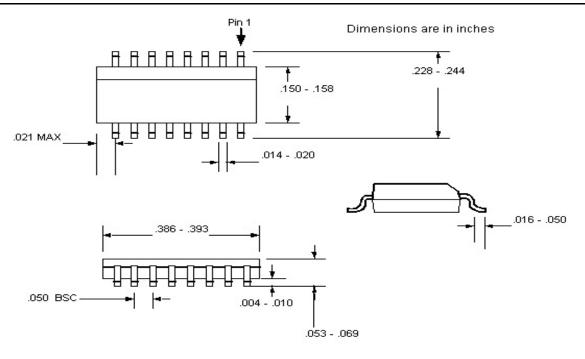

- 16 lead .150" SOIC, -55°C /+85°C

- 16 lead Ceramic 300mil SOP, -55°C /+125°C

- 100% Final Testing

SOIC package option shown

### **Functional Description:**

The DEI1026 is a six channel discrete-to-digital interface BiCMOS device. It senses six Open/Ground discrete signals of the type commonly found in avionic systems. The inverted 3-state outputs are TTL/CMOS compatible and are enabled by the  $\overline{OE}$  and  $\overline{CE}$  pins. The inputs are lightning protected to meet the requirements of DO160D Sec 22 Waveforms 3, 4, and 5, Level 3. See figures 5-7. The device is available in a 16 lead .150 SOIC and .300 Ceramic SOP.

With its reliability, low cost, operating range, and lightning protection, the DEI1026 meets a large variety of interface requirements for aerospace applications.

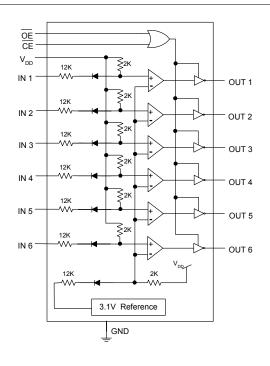

Figure 1: Concept Drawing

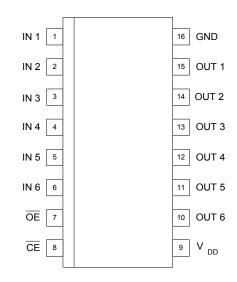

Figure 2: Pinout Diagram

| Table 1: Absolute Maximum Ratings                                                            |                    |                       |                       |       |  |  |

|----------------------------------------------------------------------------------------------|--------------------|-----------------------|-----------------------|-------|--|--|

| PARAMETER                                                                                    |                    | MIN                   | MAX                   | UNITS |  |  |

| Supply Voltage V <sub>DD</sub>                                                               |                    | -0.3                  | 7.0                   | V     |  |  |

| Discrete Input Voltage (Pins 1-6)                                                            |                    | -5                    | +40 *                 | V     |  |  |

| Digital Input Voltage (CE and OE)                                                            |                    | V <sub>SS</sub> - 0.3 | V <sub>DD</sub> + 0.3 | V     |  |  |

| Lightning Protection (Pins 1-6) DO160D, Waveform 3; Level 3 DO160D, Waveforms 4, and 5; Leve | 13                 | -600<br>-300          | +600<br>+300          | V     |  |  |

| Storage Temperature                                                                          | Plastic<br>Ceramic | -55<br>-55            | 125<br>145            | °C    |  |  |

| Operating Free Air Temperature                                                               | Plastic<br>Ceramic | -55<br>-55            | 85<br>125             | °C    |  |  |

| Lead Soldering Temperature (10 Seconds Max)                                                  |                    | -                     | 280                   | °C    |  |  |

| Body Soldering Temperature (10 Seconds Max)                                                  |                    | -                     | 210                   | °C    |  |  |

The DEI1026 contains circuitry to protect inputs from damage due to electrostatic discharge. It has been characterized per JEDEC A114-A Human Body Model to Class 1. Observe precautions for handling and storing Electrostatic Sensitive Devices.

| Table 2: DEI1026 Device Operating Characteristics |                 |                                                     |            |     |           |       |

|---------------------------------------------------|-----------------|-----------------------------------------------------|------------|-----|-----------|-------|

| PARAMETER                                         | SYMBOL          | CONDITIONS                                          | MIN        | TYP | MAX       | UNITS |

| Supply Voltage                                    | $V_{DD}$        |                                                     | 4.5        | 5.0 | 5.5       | V     |

| Free Air Operating Temp.                          | T <sub>A</sub>  | V <sub>DD</sub> = 4.5 – 5.5 V<br>Plastic<br>Ceramic | -55<br>-55 |     | 85<br>125 | °C    |

| Logic Output Sink Current                         | $I_{OL}$        | $V_{DD} = 4.5 - 5.5 \text{ V}$                      |            |     | 5.0       | mA    |

| Logic Output Source Current                       | I <sub>OH</sub> | $V_{DD} = 4.5 - 5.5 \text{ V}$                      | -5.0       |     |           | mA    |

| Table 3: DEI1026 Logic Truth Table |                    |                |        |  |  |  |

|------------------------------------|--------------------|----------------|--------|--|--|--|

| CE (Chip Enable)                   | OE (Output Enable) | Discrete Input | Output |  |  |  |

| 0                                  | 0                  | Open           | 0      |  |  |  |

| 0                                  | 0                  | Ground         | 1      |  |  |  |

| 1                                  | X                  | X              | High Z |  |  |  |

| Х                                  | 1                  | X              | High Z |  |  |  |

<sup>\*</sup> The DEI1026 will withstand the transient surge DC voltage step function loci limits for category B equipment per MIL-STD-704A.

| Table 4A: DEI1026 (Plastic) Electrical Characteristics $(T_A = -55^{\circ}C \text{ TO } +85^{\circ}C, V_{DD} = 4.5 \text{ TO } 5.5 \text{ V}, \text{ Unless otherwise noted})$ |                             |                                                                                          |                         |          |                                                |       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|------------------------------------------------------------------------------------------|-------------------------|----------|------------------------------------------------|-------|

| PARAMETER                                                                                                                                                                      | SYMBOL                      | CONDITIONS                                                                               | MIN                     | TYP      | MAX                                            | UNITS |

| Power Supply and Thermal Data                                                                                                                                                  |                             |                                                                                          |                         |          |                                                |       |

| Supply Current                                                                                                                                                                 | I <sub>DD</sub>             | $V_{IN} = V_{DD}$ (all inputs)<br>$V_{DD} = 5.5 \text{ V}$                               |                         | 5        | 10                                             | mA    |

| Thermal Resistance                                                                                                                                                             | $\theta_{JA}$ $\theta_{JC}$ | Junction to Ambient (4 layer PCB) Junction to Case                                       |                         | 74<br>24 |                                                | °C/W  |

| Max Junction Temperature                                                                                                                                                       | $T_{Jmax}$                  | Max. Junction Temperature                                                                |                         |          | 125                                            | °C    |

|                                                                                                                                                                                |                             | Discrete Input Characteristic                                                            |                         |          |                                                |       |

| Ground state input voltage                                                                                                                                                     | $V_{\text{SG}}$             | Voltage source from input terminal to ground for Logic High Output.                      |                         |          | 3.0                                            | V     |

| Open state input voltage                                                                                                                                                       | V <sub>so</sub>             | Voltage source from input terminal to ground for Logic Low Output.                       | 3.5                     |          |                                                | V     |

| Ground state input resistor                                                                                                                                                    | $R_{\text{IG}}$             | Resistor from input to ground to guarantee Logic High Output.                            | 0                       |          | 100                                            | Ω     |

| Open state input resistor                                                                                                                                                      | R <sub>IO</sub>             | Resistor from input to ground to guarantee Logic Low Output.                             | 100k                    |          |                                                | Ω     |

| Input source current                                                                                                                                                           | I <sub>IO</sub>             | Current sourced into 100 Ohm resistor to Ground.                                         | -100                    | -330     |                                                | μА    |

| Reverse leakage current                                                                                                                                                        | $I_{IR}$                    | $V_{IN} = 35 \text{ V}, \ V_{DD} = 0 \text{ V}$                                          |                         |          | 100                                            | μΑ    |

|                                                                                                                                                                                |                             | Logic Input Characteristics                                                              |                         |          |                                                |       |

| CE, OE input logic 1 level                                                                                                                                                     | V <sub>IH</sub>             | -                                                                                        | 2.0                     |          |                                                | V     |

| CE, OE input logic 0 level                                                                                                                                                     | $V_{\text{IL}}$             |                                                                                          |                         |          | 0.8                                            | V     |

|                                                                                                                                                                                |                             | <b>DC Output Characteristics</b>                                                         | ,                       |          | <u>,                                      </u> |       |

| Output logic 1 level (TTL)                                                                                                                                                     | $V_{OH}$                    | $I_{OH} = -5 \text{ mA}.$                                                                | 2.4                     |          |                                                | V     |

| Output logic 0 level (TTL)                                                                                                                                                     | $V_{OL}$                    | $I_{OL}$ = 5 mA.                                                                         |                         |          | 0.4                                            | V     |

| Output logic 1 level (CMOS)                                                                                                                                                    | $V_{OH}$                    | I <sub>OH</sub> = -100 μA                                                                | $V_{DD} - 50 \text{mV}$ |          |                                                | V     |

| Output logic 0 level (CMOS)                                                                                                                                                    | $V_{OL}$                    | I <sub>OL</sub> = 100 μA                                                                 |                         |          | V <sub>SS</sub> + 50mV                         | V     |

| Off-state Output Current                                                                                                                                                       | l <sub>oz</sub>             | $\overline{OE} = V_{DD}$<br>$V_{DD} = 5.5 \text{ V}$<br>$V_{OUT} = 0 \text{ or } V_{DD}$ |                         |          | +/-10                                          | μΑ    |

| Switching Characteristics [1]                                                                                                                                                  |                             |                                                                                          |                         |          |                                                |       |

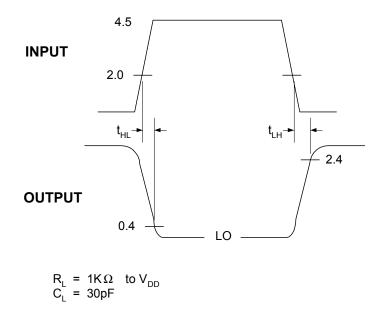

| I/O propagation delay                                                                                                                                                          | $t_{HL},t_{LH}$             | Refer to Figure 4.                                                                       |                         |          | 150                                            | ns    |

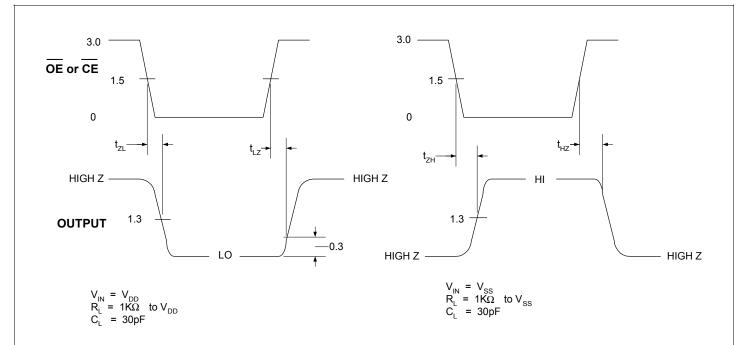

| Delay from CE or OE input (with output low) to output HI-Z                                                                                                                     | t <sub>LZ</sub>             | Refer to Figure 3.                                                                       |                         |          | 25                                             | ns    |

| Delay from CE or OE input (with output HI-Z) to output low                                                                                                                     | $t_{ZL}$                    | Refer to Figure 3.                                                                       |                         |          | 25                                             | ns    |

| Delay from CE or OE input (with output high) to output HI -Z                                                                                                                   | t <sub>HZ</sub>             | Refer to Figure 3.                                                                       |                         |          | 25                                             | ns    |

| Delay from CE or OE input (with output HI-Z) to output high                                                                                                                    | $t_{ZH}$                    | Refer to Figure 3.                                                                       |                         |          | 25                                             | ns    |

|                                                              |                                                 | -WM[ ] (Ceramic) Electr<br>C, V <sub>DD</sub> = 4.5 TO 5.5 V, U            |                        |           |                        |       |

|--------------------------------------------------------------|-------------------------------------------------|----------------------------------------------------------------------------|------------------------|-----------|------------------------|-------|

| PARAMETER                                                    | SYMBOL                                          | CONDITIONS                                                                 | MIN                    | TYP       | MAX                    | UNITS |

|                                                              |                                                 | er Supply and Thermal                                                      |                        |           |                        |       |

| Supply Current                                               | I <sub>DD</sub>                                 | V <sub>IN</sub> = V <sub>DD</sub> (all inputs)                             |                        | 5         | 10                     | mA    |

| Thermal Resistance                                           | $\theta_{JA}$                                   | V <sub>DD</sub> = 5.5 V  Junction to Ambient                               |                        | tbd<br>23 |                        | °C/W  |

| Max Junction Temperature                                     | $	heta_{	extsf{JC}} 	hinspace T_{	extsf{Jmax}}$ | Junction to Case  Max. Junction Temperature                                |                        | 23        | 145                    | °C    |

| Max deficient remperature                                    |                                                 | crete Input Characteris                                                    | tics                   |           | 140                    |       |

| Ground state input voltage                                   | V <sub>SG</sub>                                 | Voltage source from input terminal to ground for Logic High Output.        |                        |           | 3.0                    | V     |

| Open state input voltage                                     | $V_{SO}$                                        | Voltage source from input terminal to ground for Logic Low Output.         | 3.5                    |           |                        | ٧     |

| Ground state input resistor                                  | $R_{IG}$                                        | Resistor from input to ground to guarantee Logic High Output.              | 0                      |           | 100                    | Ω     |

| Open state input resistor                                    | $R_{IO}$                                        | Resistor from input to ground to guarantee Logic Low Output.               | 100k                   |           |                        | Ω     |

| Input source current                                         | I <sub>IO</sub>                                 | Current sourced into 100 Ohm resistor to Ground.                           | -100                   | -330      |                        | μΑ    |

| Reverse leakage current                                      | $I_{IR}$                                        | $V_{IN} = 35 \text{ V}, \ V_{DD} = 0 \text{ V}$                            |                        |           | 100                    | μΑ    |

|                                                              | Lo                                              | gic Input Characteristi                                                    | cs                     |           |                        |       |

| CE, OE input logic 1 level                                   | $V_{\text{IH}}$                                 |                                                                            | 2.0                    |           |                        | V     |

| CE, OE input logic 0 level                                   | $V_{IL}$                                        |                                                                            |                        |           | 0.8                    | V     |

|                                                              | D                                               | C Output Characteristic                                                    | s                      |           |                        |       |

| Output logic 1 level (TTL)                                   | $V_{OH}$                                        | I <sub>OH</sub> = -5 mA.                                                   | 2.4                    |           |                        | V     |

| Output logic 0 level (TTL)                                   | V <sub>OL</sub>                                 | I <sub>OL</sub> = 5 mA.                                                    |                        |           | 0.4                    | V     |

| Output logic 1 level (CMOS)                                  | V <sub>OH</sub>                                 | I <sub>OH</sub> = -100 μA                                                  | V <sub>DD</sub> – 50mV |           |                        | V     |

| Output logic 0 level (CMOS)                                  | $V_{OL}$                                        | I <sub>OL</sub> = 100 μA                                                   |                        |           | V <sub>SS</sub> + 50mV | V     |

| Off-state Output Current                                     | l <sub>OZ</sub>                                 | $ \overline{OE} = V_{DD}  V_{DD} = 5.5 V  V_{OUT} = 0 \text{ or } V_{DD} $ |                        |           | +/-10                  | μΑ    |

|                                                              | Sw                                              | itching Characteristics                                                    | [1]                    |           |                        |       |

| I/O propagation delay                                        | $t_{HL},t_{LH}$                                 | Refer to Figure 4.                                                         |                        |           | 170                    | ns    |

| Delay from CE or OE input (with output low) to output HI-Z   | t <sub>LZ</sub>                                 | Refer to Figure 3.                                                         |                        |           | 30                     | ns    |

| Delay from CE or OE input (with output HI-Z) to output low   | t <sub>ZL</sub>                                 | Refer to Figure 3.                                                         |                        |           | 30                     | ns    |

| Delay from CE or OE input (with output high) to output HI -Z | t <sub>HZ</sub>                                 | Refer to Figure 3.                                                         |                        |           | 30                     | ns    |

| Delay from CE or OE input (with output HI-Z) to output high  | t <sub>zH</sub>                                 | Refer to Figure 3.                                                         |                        |           | 30                     | ns    |

## Notes:

1. Guaranteed by design and not production tested.

Figure 3: Enable to Output Propagation Delay

Figure 4: Input to Output Propagation Delay

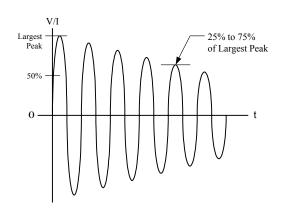

Figure 5: DO160D Voltage Waveform #3  $V_{OC}$  = 600V,  $I_{SC}$  = 24A, Frequency = 1.0MHZ ±20%

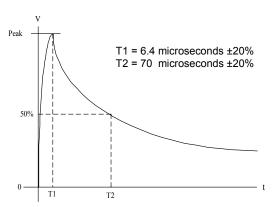

Figure 6: DO160D Voltage Waveform #4  $V_{OC}$  = 300V,  $I_{SC}$  = 60A

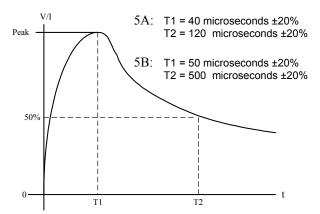

Figure 7: DO160D Voltage Waveform #5  $V_{OC}$  = 300V,  $I_{SC}$  = 300A

### Notes:

- 1. Voc = Peak Open Circuit Voltage available at the calibration point.

- 2. Isc = Peak Short Circuit Current available at the calibration point.

- 3. Amplitude tolerances: +10%, -0%

- 4. The ratio of Voc to Isc is the generator source impedance to be used for generator calibration purposes.

Figure 8: DEI1026 Mechanical Outline 16 lead 0.150" SOIC JEDEC MS-012-16

JEDEC Moisture Sensitive Rating: MSL 2

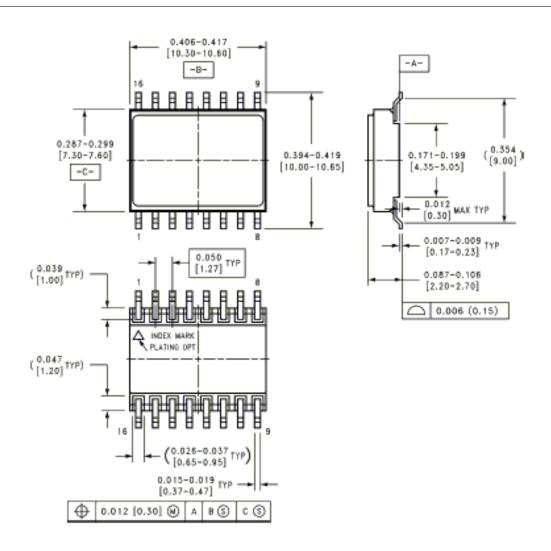

Figure 9: DEI1026-WM[] Mechanical Outline 16 lead Ceramic SOP

Table 5: Ordering Information

| DEI PART<br>NUMBER | PACKAGE                | OP. TEMP.<br>RANGE | PROCESSING               |

|--------------------|------------------------|--------------------|--------------------------|

| DEI1026            | 16 lead .150"<br>SOIC  | -55 / +85°C        | Standard                 |

| DEI1026-WMS        | 16 lead ceramic SOP    | -55 / +125°C       | Standard                 |

| DEI1026-WMB        | 16 lead ceramic<br>SOP | -55 / +125°C       | Burn In, 96 hr<br>@125°C |

DEI reserves the right to make changes to any products or specifications herein. DEI makes no warranty, representation, or guarantee regarding suitability of its products for any particular purpose.