msystems mdoc

# mDOC G4 1Gb/2Gb to mDOC H3 1Gb/2Gb

Migration Guide, Rev. 0.7

July 2006 92-UM-0905-00

## **REVISION HISTORY**

| Doc. No       | Revision | Date                                                                     | Description                                                                                                    | Reference                |

|---------------|----------|--------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--------------------------|

| 92-UM-0905-00 | 0.1      | October 2005                                                             | Initial version                                                                                                |                          |

|               | 0.2      | November 2005                                                            | mDOC H3 power management parameters updated                                                                    | Section 4.2              |

|               | 0.3      | November 2005                                                            | Electrical configuration schematics modified                                                                   | Section 4.2              |

|               | 0.4      | December 2005                                                            | Mechanical package information added                                                                           | Section 6                |

|               | 0.5      | December 2005                                                            | Core 3.3V and I/O 1.8V Electrical Configuration                                                                | Section 4.2,<br>Figure 3 |

|               |          |                                                                          | Changed location of GPIO_TIMER and JTAG RSRVD signals                                                          | Section 4.3              |

|               | 0.6      | 0.6 January 2006                                                         | Changed mechanical specification                                                                               | Section 6                |

|               |          |                                                                          | RSRVD ball assignment changes                                                                                  | Sections 4.3, 4.4        |

|               | 0.7      | 0.7 July 2006                                                            | Ordering information modified                                                                                  | Sections 1 and 3         |

|               |          |                                                                          | mDOC H3 performance updated                                                                                    | Section 3                |

|               |          |                                                                          | A note regarding top boot in mDOC H3 added                                                                     | Section 3                |

|               |          |                                                                          | Added migration path of mDOC G4 2Gb to mDOC H3 2Gb                                                             | Entire document          |

|               |          |                                                                          | DPD signal removed from mDOC<br>H3 (replaced with A0/VSS, which<br>should be connected to CPU A0 or<br>to VSS) | Sections 4.3 and 4.4     |

|               |          | RSRVD balls left floating changed from a recommendation to a requirement | Sections 4.3 and 4.4                                                                                           |                          |

|               |          |                                                                          | Standard I/F Ball H9 changed from RSRVD to VSS                                                                 | Section 4.3              |

|               |          |                                                                          | Ball G4 changed from RSRVD to VCCQ                                                                             | Sections 4.3 and 4.4     |

## **TABLE OF CONTENTS**

| 1. | Scope                                        | 4  |

|----|----------------------------------------------|----|

| 2. | Migration Requirements                       | 5  |

| 3. | Feature Comparison                           | 6  |

| 4. | mDOC G4 1Gb/2Gb to mDOC H3 1Gb/2Gb Migration | 8  |

|    | 4.1. Revising the PCB Layout                 | 8  |

|    | 4.2. mDOC G4 and H3 Power Management         | 8  |

|    | 4.3. Standard Interface                      | 12 |

|    | 4.3.1. Ballout                               | 12 |

|    | 4.3.2. Signal Description                    | 13 |

|    | 4.4. Multiplexed Interface                   | 16 |

|    | 4.4.1. Ballout                               | 16 |

|    | 4.4.2. Signal Description                    | 17 |

| 5. | Timing Specifications                        | 21 |

| 6. | Mechanical Dimensions                        | 22 |

| 7. | Software Changes                             | 23 |

| 8. | Additional Information                       | 24 |

| Нο | ow to Contact Us                             | 25 |

### 1. SCOPE

mDOC H3 is the next generation of the mDOC family of products, consisting of a new controller and advanced NAND technology flash. mDOC H3 products are packaged in a FBGA package that is ball to ball compatible with the mDOC G4 product lines. mDOC H3 introduces easier storage integration and boot implementation, multiple sources and a wide range of densities from 1Gb to 16Gb in 2006.

This guide describes the hardware-related guidelines for migrating from mDOC G4 1Gb and 2Gb 9x12mm devices to mDOC H3 1Gb and 2Gb 9x12 devices.

mDOC G4 1Gb, mDOC G4 2Gb, mDOC H3 1Gb and mDOC H3 2Gb ordering information is provided in Table 1.

| Product | Capacity                                      | Ordering Information |

|---------|-----------------------------------------------|----------------------|

|         | 128MByte (1Gbit)<br>1.8V core                 | MD8832-d1G-V18-X-P   |

| mDOC C4 | 128MByte (1Gbit)<br>3.3V core                 | MD8832-d1G-V3-X-P    |

| mDOC G4 | 256MByte (2Gbit)<br>1.8V core                 | MD8331-d2G-V18-X-P   |

|         | 256MByte (2Gbit)<br>3.3V core                 | MD8331-d2G-V3-X-P    |

| ~DOC U2 | 128MByte (1Gbit)<br>3.3V/1.8V core and<br>I/O | MD2534-d1G-X-P       |

| mDOC H3 | 256MByte (2Gbit)<br>3.3V/1.8V core and        | MD2534-d2G-X-P       |

Table 1: mDOC G4 and mDOC H3- Ordering information

Note: Throughout this guide, product capacities will be referred to in Mbit (Mb), Gbit (Gb) MByte (MB), and GByte (GB).

# msystems

### 2. MIGRATION REQUIREMENTS

It is possible to migrate from the mDOC G4 1Gb and 2Gb devices to mDOC H3 1Gb and 2Gb devices. All mDOC products are ball-to-ball compatible.

Designers should focus on the following issues when migrating between mDOC products:

- Revising the PCB layout (Section 4.1): mDOC H3 introduces some additional signals which are not available in mDOC G4. It is possible to design the PCB to accommodate a dual footprint for both mDOC H3 and G4 due to the ball to ball compatibility.

- Timing verification (Section 5): mDOC H3 product line has new timing specifications.

- Software changes (Section 7): mDOC H3 requires an updated version of TrueFFS.

Please note that mDOC G4 1Gb and 2Gb have 69 balls while the mDOC H3 1Gb and 2Gb devices have 115 balls. The migration path described in this document defines a combined, 115 ball foot print that accommodates both devices.

## 3. FEATURE COMPARISON

Table 2 compares the features offered by mDOC G4 1Gb to those offered by mDOC H3 1Gb.

Table 2: Feature List for mDOC G4 1Gb vs. H3 1Gb Product

| Features                                                                           | mDO                                      | C G4                                    | mDC                                       | DC H3                                     |

|------------------------------------------------------------------------------------|------------------------------------------|-----------------------------------------|-------------------------------------------|-------------------------------------------|

|                                                                                    | mDOC G4 1Gb                              | mDOC G4 2Gb                             | mDOC H3 1Gb                               | mDOC H3 2Gb                               |

| Ordering<br>Information                                                            | MD8832-d1G-V18-X-P,<br>MD8832-d1G-V3-X-P | MD8331-d2G-V18-X-P<br>MD8331-d2G-V3-X-P | MD2534-d1G-X-P                            | MD2534-d2G-X-P                            |

| NAND Process (nm)                                                                  | 90                                       | 90                                      | 70                                        | 70                                        |

| Form Factor (mm)<br>Total Number of<br>Balls                                       | 9x12x1.2 FBGA<br>69 balls                | 9x12x1.2 FBGA<br>69 balls               | 9x12 x1.2 FBGA<br>115 balls               | 9x12 x1.2 FBGA<br>115 balls               |

| Asynchronous<br>Boot Mode                                                          | <b>V</b>                                 | V                                       | <b>V</b>                                  | <b>V</b>                                  |

| Interface:<br>NOR-<br>like/Multiplexed                                             | <b>NN</b>                                | <b>NN</b>                               | <b>N</b> N                                | <b>1/1</b>                                |

| Interface:<br>Serial SPI                                                           | -                                        | -                                       | <b>√</b>                                  | <b>V</b>                                  |

| Boot Block (KB)                                                                    | 2                                        | 2                                       | 32²                                       | 32²                                       |

| Security and<br>Protection<br>Features (OTP,<br>unique ID,<br>protected partition) | <b>V</b>                                 | <b>V</b>                                | <b>V</b>                                  | <b>V</b>                                  |

| Cascading<br>(Maximum Number<br>of Devices)                                        | 4                                        | 2                                       | 2                                         | 2                                         |

| EDC/ECC                                                                            | BCH & Hamming 4-bit                      | BCH & Hamming 4-bit                     | BCH 6-bit                                 | BCH 6-bit                                 |

| 8 bit Bus Width                                                                    | $\checkmark$                             | $\checkmark$                            | -                                         | -                                         |

| 16 bit Bus Width                                                                   | V                                        | √                                       | $\checkmark$                              | $\checkmark$                              |

|                                                                                    | Power Requir                             | ements (Typical Para                    | ımeters)                                  |                                           |

| Core / I/O<br>Operation Voltage<br>(VCC/VCCQ) (V)                                  | 3.3/3.3; 3.3/1.8<br>1.8/1.8              | 3.3/3.3; 3.3/1.8<br>1.8/1.8             | 3.3/3.3; 3.3/1.8<br>1.8/1.8               | 3.3/3.3; 3.3/1.8<br>1.8/1.8               |

| Typical Current<br>Requirement per<br>Operation (Icc)<br>(mA)                      | Read 4.2<br>Program 7.4<br>Erase 7.4     | Read 4.2<br>Program 7.4<br>Erase 7.4    | Turbo Mode – 30<br>PowerSave Mode<br>- 20 | Turbo Mode – 30<br>PowerSave Mode -<br>20 |

| Typical Deep<br>Power Down<br>Current (Iccs) (µA)                                  | 10                                       | 20                                      | 45                                        | 45                                        |

| Features                 | mDOC G4 mDOC H3                |     |             | OC H3       |  |  |  |

|--------------------------|--------------------------------|-----|-------------|-------------|--|--|--|

|                          | mDOC G4 1Gb mDOC G4 2Gb mDOC H |     | mDOC H3 1Gb | mDOC H3 2Gb |  |  |  |

|                          | Performance                    |     |             |             |  |  |  |

| Sustained Write (MB/sec) | 2.4                            | 2.4 | 5-7         | 5-7         |  |  |  |

| Sustained Read (MB/sec)  | 10                             | 10  | 15-25       | 15-25       |  |  |  |

Note: the "\$\sqrt{n}\$ symbol indicates that a feature is implemented.

Up to 32KB may be used when using 128KB memory window (connecting A13-A16). Up to 2KB may be used when using 8KB memory window (connecting A13-A16 not required). When using 8KB memory window, only boot from lowest mDOC address (mDOC base) address, typically address zero) is supported. Boot from top address (mDOC base address + 0x1ffe) is not supported, as mDOC top address range (0x1800-0x1ffe) does not alias IPL in this mode.

## 4. MDOC G4 1GB/2GB TO MDOC H3 1GB/2GB MIGRATION

## 4.1. Revising the PCB Layout

mDOC H3 is ball to ball compatible with mDOC G4.

However when migrating from mDOC G4 1Gb or 2Gb 9x12mm to mDOC H3 1Gb or 2Gb 9x12mm products:

- Changes must be made to account for the increase in the number of balls (from 69 in G4 to 115 in H3).

- New signal routing is required for the PCB, to support the additional signals of mDOC H3.

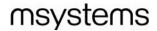

The following sections describe the ballout and signal descriptions of the standard and multiplexed interfaces (of both mDOC G4 and mDOC H3 devices). DPD Signal in mDOC G4 and mDOC H3

DPD Signal is relevant for the mDOC G4 product line only. When enabled, the DPD input is used to enter/exit Deep Power-Down mode. Depending on the settings in the DPD register, it can be used to enter or exit upon either assertion or negation.

For mDOC H3 devices this signal is not used. The DPD functionality is activated via SW, and no HW support is required. In case this signal is pulled high during mDOC H3 normal work, some functionality is disabled. Please refer to *Errata for mDOC H3 and mDOC H3-Based MCPs* for further information.

Figure 1 below describes a possible single PCB design to support both mDOC G4 and mDOC H3.

Figure 1: Single PCB Design for mDOC G4 and mDOC H3

- When mDOC H3 is used, the R2 ball should be connected (zero value resistor) and the R1 ball should be disconnected. This way A0/DPD signal is always low for mDOC H3 and mDOC H3-based MCPs.

- When mDOC G4 is used, the R1 ball should be connected (zero value resistor) and the R2 ball should be disconnected. This way A0/DPD signal can still be pulled low when taking mDOC out of DPD.

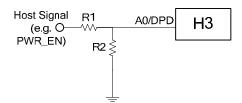

## 4.2. mDOC G4 and H3 Power Management

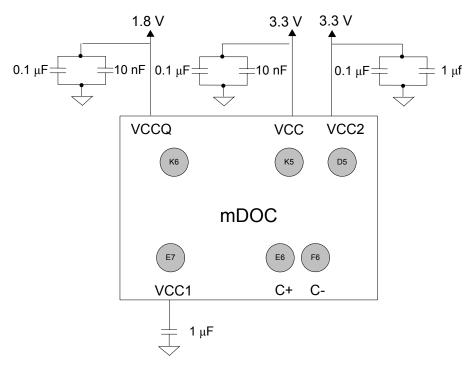

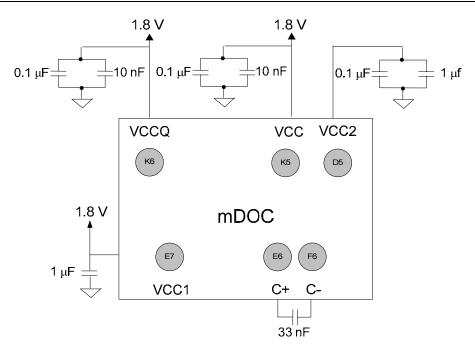

mDOC G4 and H3 share the same Device IO power supply (VCCQ) signals. mDOC H3 requires additional device controller supply connectivity as shown below:

# msystems

| Signal | Ball No. | Description                                                                                                                                                                                |

|--------|----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VCCQ   | K6 , G4  | I/O power supply. Ball K6 requires a 10 nF and 0.1 µF capacitor.                                                                                                                           |

| VCC    | K5       | mDOC Device supply. Requires a 10 nF and 0.1 μF capacitor.                                                                                                                                 |

| VCC1   | E7       | mDOC H3 internal supply. Requires a 1µF capacitor.  Note: If 1.8V VCC supply is not available this ball should be connected to a 1uF capacitor only.                                       |

| VCC2   | D5       | mDOC H3 internal supply. Requires a 1 $\mu$ F and 0.1 $\mu$ F capacitor. Note: If 3.3V supply is not available this ball should be connected to 1 $\mu$ F and 0.1 $\mu$ F capacitors only. |

| C+, C- | E6, F6   | mDOC H3 requires a 33nF capacitor connected between the C+ and C-signals.                                                                                                                  |

mDOC devices can be configured to support different combinations of Core and IO host supply. When migrating from mDOC G4 to H3, additional power supply connectivity of mDOC H3 should be added.

Table 4 lists the connectivity required for the support of the different available combinations.

Table 4: mDOC Core and IO Power Supply Connectivity

| mDOC power<br>Supply      | VCC<br>(Ball K5)    | VCCQ<br>(Ball K6 , G4) | VCC1<br>(Ball E7)        | VCC2<br>(Ball D5) | C+, C-<br>(Balls E6, F6)  |

|---------------------------|---------------------|------------------------|--------------------------|-------------------|---------------------------|

| Core: 3.3V<br>[2.7V-3.6V] | 3.3V<br>[2.7V-3.6V] | 3.3V                   | Requires a 1uF capacitor | 3.3V              | No Connection             |

| IO: 3.3V                  | [2.7 V-3.0 V]       | [2.5V-3.6V]            | only                     | [2.7V-3.6V]       |                           |

| [2.5V-3.6V]               |                     |                        | ,                        |                   |                           |

| Core: 3.3V                |                     |                        |                          |                   |                           |

| [2.7V-3.6V]               | 3.3V                | 1.8V                   | Requires a               | 3.3V              | No Connection             |

| IO: 1.8V                  | [2.7V-3.6V]         | [1.65V-1.95V]          | 1uF capacitor only]      | [2.7V-3.6V]       | No Connection             |

| [1.65V-1.95V]             |                     |                        | S, <sub>1</sub>          |                   |                           |

| Core: 1.8V                |                     |                        |                          | Requires a        |                           |

| [1.65V-1.95V]             | 1.8V                | 1.8V                   | 1.8V                     | 1uF and 0.1       | requires a 33nF capacitor |

| IO: 1.8V                  | [1.65V-1.95V]       | [1.65V-1.95V]          | [1.65V-1.95V]            | μF capacitor      | Capacitoi                 |

| [1.65V-1.95V]             |                     |                        |                          | only              |                           |

Figure 2, Figure 3 and Figure 4 provide a schematic view of the connectivity required for the different core and IO voltages.

Figure 2: Core 3.3V and IO 3.3V Electrical Configuration

Figure 3: Core 3.3V and IO 1.8V Electrical Configuration

Figure 4: Core 1.8V and IO 1.8V Electrical Configuration

#### 4.3. Standard Interface

#### 4.3.1. **Ballout**

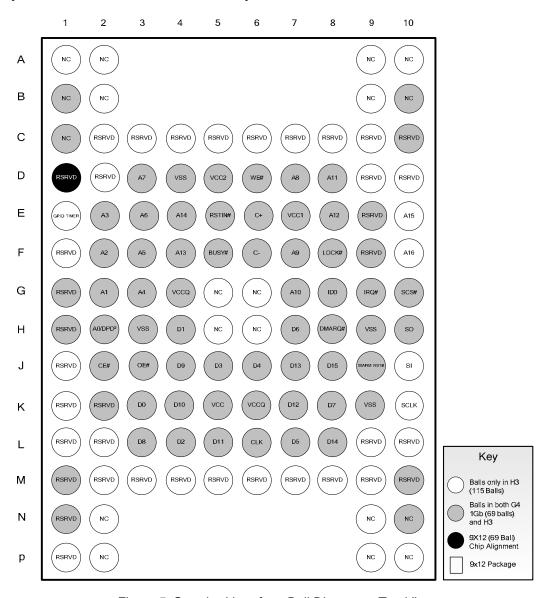

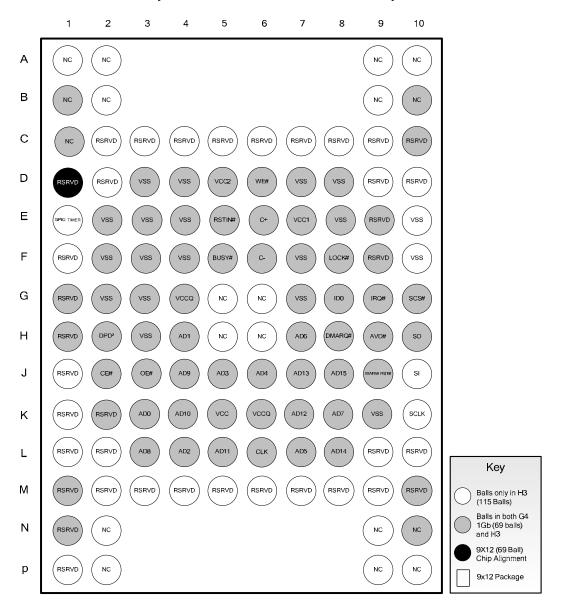

Figure 5 shows a top view of the ballout for the standard interface upgrade path from mDOC G4 1Gb/2Gb 9x12mm 69 ball to mDOC H3 1Gb/2Gb 9x12mm 115 ball.

Note: The balls highlighted in grey represent the balls of the mDOC G4 1Gb/2Gb device (69 balls). The white balls represent the balls added in mDOC H3 1Gb/2Gb (115 balls). The black ball represents an alignment identifier in the 69 ball layout that is a reserved ball in the 115 ball layout.

Figure 5: Standard Interface Ball Diagram - Top View

Notes: 1. Ball D1 is the 9x12 package (69 ball) chip alignment ball. C1 is the 9x12 and 12x18 package (115 ball) chip alignment ball (no ball).

2. Please refer to section 4.1 for further details regarding how to connect ball H2.

3. Ball G4 must be connected to VCCQ. Connecting this ball to capacitors is not mandatory (can be connected same as IF\_CFG signal on mDOC G3/P3, mDOC G3/P3 LP, mDOC G4 and mDOC H1).

## 4.3.2. Signal Description

All mDOC products specified in this document are ball to ball compatible.

The ball designations are listed in the signal descriptions, presented in logic groups, in Table 5.

Table 5: Standard Interface Signal Description

| Signal                                  | Ball No.                                                 | Description                                                                                                                                                                                                                                                                          | G4<br>69 Balls | H3<br>115 Balls                                                                                                    |  |  |  |

|-----------------------------------------|----------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------------------------------------------------------------------------------------------------------------------|--|--|--|

|                                         | System Interface                                         |                                                                                                                                                                                                                                                                                      |                |                                                                                                                    |  |  |  |

| A[16:15]<br>A[14:13]                    | F10, E10<br>E4, F4                                       | Address bus. If not used may be left floating.                                                                                                                                                                                                                                       | -              | √                                                                                                                  |  |  |  |

| A[12:11]<br>A[10:8]<br>A[7:4]<br>A[3:0] | E8, D8<br>G7, F7, D7<br>D3, E3, F3, G3<br>E2, F2, G2, H2 | Address bus.                                                                                                                                                                                                                                                                         | V              | V                                                                                                                  |  |  |  |

| D[7:6]<br>D[5:3]<br>D[2:0]              | K8, H7<br>L7, J6, J5<br>L4, H4, K3                       | Data bus, low byte.                                                                                                                                                                                                                                                                  | $\checkmark$   | √                                                                                                                  |  |  |  |

| D[15:14]<br>D[13:12]<br>D[11:8]         | J8, L8<br>J7, K7<br>L5, K4, J4, L3                       | Data bus, high byte.                                                                                                                                                                                                                                                                 | V              | √.                                                                                                                 |  |  |  |

| CE#                                     | J2                                                       | Chip Enable, active low.                                                                                                                                                                                                                                                             | $\sqrt{}$      | $\sqrt{}$                                                                                                          |  |  |  |

| OE#                                     | J3                                                       | Output Enable, active low.                                                                                                                                                                                                                                                           | <b>√</b>       | $\sqrt{}$                                                                                                          |  |  |  |

| WE#                                     | D6                                                       | Write Enable, active low.                                                                                                                                                                                                                                                            | √              | <b>√</b>                                                                                                           |  |  |  |

|                                         |                                                          | Configuration                                                                                                                                                                                                                                                                        |                |                                                                                                                    |  |  |  |

| GPIO_TIMER                              | E1                                                       | mDOC H3 GPIO or configurable timer. If not used may be left floating.                                                                                                                                                                                                                | -              | $\sqrt{}$                                                                                                          |  |  |  |

| ID[1:0]                                 | H9, G8                                                   | Identification. Configuration control to support up to four chips cascaded in the same memory window.  Chip 1: ID1, ID0 = VSS, VSS (0,0); required for single chip as well.  Chip 2: ID1, ID0 = VSS, VCC (0,1)  Chip 3: ID1, ID0 = VCC, VSS (1,0)  Chip 4: ID1, ID0 = VCC, VCC (1,1) | V              | -/√ mDOC H3 support cascading of up to 2 devices only. In this case ID1 is not used, and must be connected to VSS. |  |  |  |

| IF_CFG                                  | G4                                                       | Interface Configuration. Set to 1 (VCCQ) for 16-bit interface mode. Clear to 0 (VSS) for 8-bit interface mode.                                                                                                                                                                       | V              | -/√ mDOC<br>H3 support<br>only 16 bit<br>interface.<br>This signal<br>must be<br>connected                         |  |  |  |

| Cianal    | Dell No  | Description                                                                                                                                                                                                                                                                | G4        | Н3                                                |

|-----------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|---------------------------------------------------|

| Signal    | Ball No. | Description                                                                                                                                                                                                                                                                | 69 Balls  | 115 Balls                                         |

|           |          |                                                                                                                                                                                                                                                                            |           | to VCCQ                                           |

| LOCK#     | F8       | Lock, active low. When active, provides full hardware data protection of selected partitions.                                                                                                                                                                              | √         | √                                                 |

|           |          | Control                                                                                                                                                                                                                                                                    |           |                                                   |

| WARM_RST# | J9       | mDOC H3 Warm reset input, used for triggering device warm-reset. Active low. If not used may be left floating.                                                                                                                                                             | -         | V                                                 |

| BUSY#     | F5       | Busy. Active low, open drain. Indicates that mDOC is initializing and should not be accessed. A pull-up resistor to VCCQ is required if this ball drives an input. A pull-up resistor is recommended even if this ball is not used (resistor value depends on the system). | V         | V                                                 |

| RSTIN#    | E5       | Reset, active low.                                                                                                                                                                                                                                                         | <b>V</b>  | √                                                 |

| CLK       | L6       | External clock input used for burst mode data transfers. If not used may be left floating.                                                                                                                                                                                 | <b>V</b>  | √                                                 |

| DMARQ#    | H8       | DMA request. Active low. A pull-up resistor to VCCQ is required if this ball drives an input. A pull-up resistor is recommended even if this ball is not used (resistor value depends on the system).                                                                      | V         | <b>V</b>                                          |

| IRQ#      | G9       | Interrupt Request. Active low. A pull-up resistor to VCCQ is required if this ball drives an input. A pull-up resistor is recommended even if this ball is not used (resistor value depends on the system).                                                                | V         | <b>V</b>                                          |

| DPD       | H2       | When IF_CFG=1(16bit), the device can be programmed to use this input to enter or exit DPD mode.                                                                                                                                                                            | <b>√</b>  | Not used<br>on mDOC<br>H3 (see<br>section<br>4.1) |

|           |          | Serial Interface                                                                                                                                                                                                                                                           |           |                                                   |

| SCS#      | G10      | Serial Interface chip select. Active low. If not used may be left floating.                                                                                                                                                                                                | -         | √                                                 |

| SO        | H10      | Serial Interface data out (In Serial slave mode) <sup>1</sup> . If not used may be left floating.                                                                                                                                                                          | -         | √                                                 |

| SI        | J10      | Serial Interface data in (In serial slave mode) <sup>1</sup> . If not used may be left floating.                                                                                                                                                                           | -         | √                                                 |

| SCLK      | K10      | Serial Interface clock. If not used may be left floating.                                                                                                                                                                                                                  | -         | √                                                 |

|           |          | Power                                                                                                                                                                                                                                                                      |           |                                                   |

| VCC2      | D5       | mDOC H3 internal supply. Requires a 1μF and 0.1 μF capacitor.                                                                                                                                                                                                              | -         | √                                                 |

| VCC1      | E7       | mDOC H3 internal supply. Requires a 1µF capacitor.                                                                                                                                                                                                                         | -         | √                                                 |

| VCCQ      | K6, G4   | I/O power supply. Ball K6 requires a 10 nF and 0.1 µF capacitor.                                                                                                                                                                                                           | √/-       | <b>V/V</b>                                        |

| VCC       | K5       | Device supply. Requires a 10 nF and 0.1 μF                                                                                                                                                                                                                                 | $\sqrt{}$ | $\sqrt{}$                                         |

| Signal | Ball No.                                                                                                                                                            | Description                                                                                                                                                                                                                                                                                                                          | G4<br>69 Balls | H3<br>115 Balls |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|-----------------|--|--|--|

|        |                                                                                                                                                                     | capacitor.                                                                                                                                                                                                                                                                                                                           |                |                 |  |  |  |

| VSS    | D4, H3, H9, K9                                                                                                                                                      | Ground. All VSS balls must be connected.                                                                                                                                                                                                                                                                                             | √              | √               |  |  |  |

| C+     | E6                                                                                                                                                                  | C1 - 33nF capacitor positive terminal <sup>2</sup> .                                                                                                                                                                                                                                                                                 | -              | $\sqrt{}$       |  |  |  |

| C-     | F6                                                                                                                                                                  | C1 - 33nF capacitor negative terminal <sup>2</sup> .                                                                                                                                                                                                                                                                                 | -              | √               |  |  |  |

|        |                                                                                                                                                                     | Reserved                                                                                                                                                                                                                                                                                                                             |                |                 |  |  |  |

| RSRVD  | C2, C3, C4,<br>C5, C6, C7,<br>C8, C9, C10,<br>D1, D2, D9,<br>D10, E9, F1,<br>F9, G1, H1,<br>J1, K1, K2, L2,<br>L9, L10, M2,<br>M3, M4, M5,<br>M6,M7, M8,<br>M9, M10 | Reserved signal that is not connected internally.  All reserved signals are not connected internally, and if not identified in this document then it is recommended to leave them floating to guarantee forward compatibility with future products. They should not be connected to arbitrary signals and must not be left floating. | V              | <b>V</b>        |  |  |  |

|        | P1                                                                                                                                                                  | Test Data In (JTAG). Used for dedicated developer product only <sup>3</sup> .                                                                                                                                                                                                                                                        | -              | <b>√</b>        |  |  |  |

|        | M1                                                                                                                                                                  | Test Data Out (JTAG). Used for dedicated developer product only <sup>3</sup> .                                                                                                                                                                                                                                                       | -              | √               |  |  |  |

|        | L1                                                                                                                                                                  | Test Mode Select (JTAG). Used for dedicated developer product only <sup>3</sup> .                                                                                                                                                                                                                                                    | -              | V               |  |  |  |

|        | N1                                                                                                                                                                  | Test Clock (JTAG). Used for dedicated developer product only <sup>3</sup> .                                                                                                                                                                                                                                                          | -              | <b>√</b>        |  |  |  |

|        | Mechanical                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                      |                |                 |  |  |  |

| NC     | A1, A2, A9,<br>A10, B1, B2,<br>B9, C1, B10,<br>G5, G6, H5,<br>H6, N2, N9,<br>N10, P2, P9,<br>P10                                                                    | Not Connected.                                                                                                                                                                                                                                                                                                                       |                |                 |  |  |  |

- 1. When mDOC H3 is used as a Master device, SO is used for Serial Interface Data In, and SI is used for Serial Interface Data Out.

- 2. The 33 nF capacitor is required only for 1.8V Core and 1.8V I/O configuration. Please see section 4.2 for further details.

- 3. The RSRVD JTAG balls will only be enabled on special versions of the mDOC H3 devices that will be used for debugging severe system problems. In order to support this feature, the JTAG balls should be brought out to a separate header or test points. The JTAG RSRVD balls must not be connected to the JTAG scan chain that is used for the rest of the PCB. If not used they should be left floating.

## 4.4. Multiplexed Interface

#### 4.4.1. **Ballout**

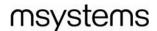

Figure 6 shows a top view of the ballout for the multiplexed interface upgrade path from mDOC G4 1Gb/2Gb 9x12 mm 69 ball to mDOC H3 1Gb/2Gb 9x12 115 ball.

Note: The balls highlighted in grey represent the balls of the mDOC G4 device (69 balls). The white balls represent the balls added in mDOC H3 (115 balls). The added balls are all dummy balls. The black ball represents an alignment identifier in the 69 ball layout that is a reserved ball in the 115 ball layout.

Figure 6: Multiplexed Interface Ball Diagram for FBGA - Top View

Notes: 1. Ball D1 is the 9x12 package (69 ball) chip alignment ball. C1 is the 9x12 and 12x18 package (115 ball) chip alignment ball (no ball).

2. Please refer to section 4.1 for further details regarding how to connect this ball.

3. Ball G4 must be connected to VCCQ. Connecting this ball to capacitors is not mandatory (can be connected same as IF\_CFG signal on mDOC G3/P3, mDOC G3/P3 LP, mDOC G4 and mDOC H1).

## 4.4.2. Signal Description

All mDOC products specified in this document support common interface signals.

The ball designations are listed in the signal descriptions, presented in logic groups, in Table 6.

Table 6: Multiplexed Interface Signal Description

| 0:                                          | D.U.M.                                                              | Bernduden                                                                                                                                                                                                                                                                  | G4           | Н3        |  |  |  |

|---------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|-----------|--|--|--|

| Signal                                      | Ball No.                                                            | Description                                                                                                                                                                                                                                                                | 69 Balls     | 115 Balls |  |  |  |

|                                             | System Interface                                                    |                                                                                                                                                                                                                                                                            |              |           |  |  |  |

| AD[15:12]<br>AD[11:8]<br>AD[7:4]<br>AD[3:0] | J8, L8, J7, K7<br>L5, K4, J4, L3<br>K8, H7, L7,J6<br>J5, L4, H4, K3 | Multiplexed bus. Address and data signals.                                                                                                                                                                                                                                 | V            | V         |  |  |  |

| CE#                                         | J2                                                                  | Chip Enable, active low.                                                                                                                                                                                                                                                   | √            | √         |  |  |  |

| OE#                                         | J3                                                                  | Output Enable, active low.                                                                                                                                                                                                                                                 | √            | √         |  |  |  |

| WE#                                         | D6                                                                  | Write Enable, active low.                                                                                                                                                                                                                                                  | √            | √         |  |  |  |

|                                             |                                                                     | Configuration                                                                                                                                                                                                                                                              |              |           |  |  |  |

| GPIO_TIMER                                  | E1                                                                  | mDOC H3 GPIO or a configurable timer. If not used may be left floating.                                                                                                                                                                                                    | -            | $\sqrt{}$ |  |  |  |

| AVD#                                        | H9                                                                  | Address Valid strobe. Set multiplexed interface.                                                                                                                                                                                                                           | $\sqrt{}$    | <b>√</b>  |  |  |  |

| ID0                                         | G8                                                                  | Identification. Configuration control to support up to two chips cascaded in the same memory window.  Chip 1: ID0 = VSS, must be used for single-chip configuration.  Chip 2: ID0 = VCCQ.                                                                                  | <b>V</b>     | <b>V</b>  |  |  |  |

| LOCK#                                       | F8                                                                  | Lock. Active low. When active, provides full hardware data protection of selected partitions.                                                                                                                                                                              | V            | V         |  |  |  |

|                                             |                                                                     | Control                                                                                                                                                                                                                                                                    |              |           |  |  |  |

| WARM_RST#                                   | J9                                                                  | Active low. Warm reset input, used for triggering device warm-reset. If not used may be left floating.                                                                                                                                                                     | -            | V         |  |  |  |

| BUSY#                                       | F5                                                                  | Busy. Active low, open drain. Indicates that mDOC is initializing and should not be accessed. A pull-up resistor to VCCQ is required if this ball drives an input. A pull-up resistor is recommended even if this ball is not used (resistor value depends on the system). | V            | V         |  |  |  |

| RSTIN#                                      | E5                                                                  | Reset, active low.                                                                                                                                                                                                                                                         | $\checkmark$ | $\sqrt{}$ |  |  |  |

| Ciam al | 5 " "                                                                                          | <b>5</b>                                                                                                                                                                                                    | G4       | Н3                                                |

|---------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|---------------------------------------------------|

| Signal  | Ball No.                                                                                       | Description                                                                                                                                                                                                 | 69 Balls | 115 Balls                                         |

| CLK     | L6                                                                                             | External clock input used for burst mode data transfers. If not used may be left floating.                                                                                                                  | V        | V                                                 |

| DMARQ#  | H8                                                                                             | DMA request. Open drain. A pull-up resistor to VCCQ is required if this ball drives an input. A pull-up resistor is recommended even if this ball is not used (resistor value depends on the system).       | V        | V                                                 |

| IRQ#    | G9                                                                                             | Interrupt Request. Active low. A pull-up resistor to VCCQ is required if this ball drives an input. A pull-up resistor is recommended even if this ball is not used (resistor value depends on the system). | <b>V</b> | V                                                 |

| DPD     | H2                                                                                             | Device can be programmed to use this input to enter or exit DPD mode.                                                                                                                                       | V        | Not used<br>on mDOC<br>H3 (see<br>section<br>4.2) |

|         |                                                                                                | Serial Interface                                                                                                                                                                                            |          |                                                   |

| SCS#    | G10                                                                                            | Serial Interface chip select. Active Low. If not used may be left floating.                                                                                                                                 | -        | <b>√</b>                                          |

| SO      | H10                                                                                            | Serial Interface data out (In Serial slave mode) <sup>1</sup> . If not used may be left floating.                                                                                                           | -        | <b>√</b>                                          |

| SI      | J10                                                                                            | Serial Interface data in (In serial slave mode) <sup>1</sup> . If not used may be left floating.                                                                                                            | -        | <b>√</b>                                          |

| SCLK    | K10                                                                                            | Serial Interface clock. If not used may be left floating.                                                                                                                                                   | -        | <b>√</b>                                          |

|         | 1                                                                                              | Power                                                                                                                                                                                                       | T        | 1                                                 |

| VCC2    | D5                                                                                             | mDOC H3 internal supply. Requires a 1μF and 0.1 μF capacitor.                                                                                                                                               | -        | V                                                 |

| VCC1    | E7                                                                                             | mDOC H3 internal supply. Requires a 1μF capacitor.                                                                                                                                                          | -        | <b>√</b>                                          |

| VCCQ    | K6, G4                                                                                         | I/O power supply. Ball K6 requires a 10 nF and 0.1 µF capacitor.                                                                                                                                            | √/√      | √/√                                               |

| VCC     | K5                                                                                             | Device supply. Requires a 10 nF and 0.1 µF capacitor.                                                                                                                                                       | <b>√</b> | <b>√</b>                                          |

| VSS     | D3, D4, D7,<br>D8, E2, E3,<br>E4 E8, E10,<br>F2, F3, F4,<br>F7, F10, G2,<br>G3, G7, H3,<br>K9, | Ground. All VSS balls must be connected.                                                                                                                                                                    | V        | V                                                 |

| C+      | E6                                                                                             | C1 - 33nF capacitor positive terminal <sup>2</sup> .                                                                                                                                                        | -        | <b>V</b>                                          |

| Signal | Ball No. | Description                                          | G4<br>69 Balls | H3<br>115 Balls |

|--------|----------|------------------------------------------------------|----------------|-----------------|

| C-     | F6       | C1 - 33nF capacitor negative terminal <sup>2</sup> . | -              | $\sqrt{}$       |

| 0:- :      | D-II N                                                                                                                                               | Beaut ii                                                                                                                                                                                                                                                                                                                            | G4       | Н3        |  |

|------------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|-----------|--|

| Signal     | Ball No.                                                                                                                                             | Description                                                                                                                                                                                                                                                                                                                         | 69 Balls | 115 Balls |  |

| Reserved   |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                     |          |           |  |

| RSRVD      | C2, C3, C4,                                                                                                                                          | Decembed signal that is not connected                                                                                                                                                                                                                                                                                               | RSRVD    | RSRVD     |  |

|            | C5, C6, C7,<br>C8, C9, C10,<br>D1, D2, D9,<br>D10, E9, F1,<br>F9, G1, H1,<br>J1, K1, K2,<br>L2, L9, L10,<br>M2, M3, M4,<br>M5, M6,M7,<br>M8, M9, M10 | Reserved signal that is not connected internally.  All reserved signals are not connected internally and if not identified in this document then it is recommended to leave them floating to guarantee forward compatibility with future products. They should not be connected to arbitrary signals and must not be left floating. | V        | V         |  |

|            | P1                                                                                                                                                   | Test Data In (JTAG).  Used for dedicated developer product only <sup>3</sup> .                                                                                                                                                                                                                                                      | -        | <b>V</b>  |  |

|            | M1                                                                                                                                                   | Test Data Out (JTAG).  Used for dedicated developer product only <sup>3</sup> .                                                                                                                                                                                                                                                     | -        | V         |  |

|            | L1                                                                                                                                                   | Test Mode Select (JTAG).  Used for dedicated developer product only <sup>3</sup> .                                                                                                                                                                                                                                                  | -        | <b>V</b>  |  |

|            | N1                                                                                                                                                   | Test Clock (JTAG) Used for dedicated developer product only <sup>3</sup> .                                                                                                                                                                                                                                                          | -        | V         |  |

| Mechanical |                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                     |          |           |  |

| NC         | A1, A2, A9,<br>A10, B1, B2,<br>B9, B10, C1,<br>G5, G6, H5,<br>H6, N2, N9,<br>N10, P2, P9,<br>P10                                                     | Not Connected.                                                                                                                                                                                                                                                                                                                      |          |           |  |

<sup>1.</sup> When mDOC H3 is used as a Master device, SO is used for Serial Interface Data In, and SI is used for Serial Interface Data Out.

<sup>2.</sup> The 33 nF capacitor is required only for 1.8V Core and 1.8V I/O configuration. Please see section 4.2 for further details.

<sup>3.</sup> The RSRVD JTAG balls will only be enabled on special versions of the mDOC H3 devices that will be used for debugging severe system problems. In order to support this feature, the JTAG balls should be brought out to a separate header or test points. The JTAG RSRVD balls must not be connected to the JTAG scan chain that is used for the rest of the PCB.

## 5. TIMING SPECIFICATIONS

When reviewing the timing specifications during the migration design, the following should be taken into account:

- Timing specifications for mDOC G4 standard and multiplexed interface read/write cycles are not identical to the timing specifications for mDOC H3 devices.

- When designing for compatibility between several mDOC devices, the worst-case timing should be used.

- For further information, see the product data sheets for mDOC G4 and mDOC H3.

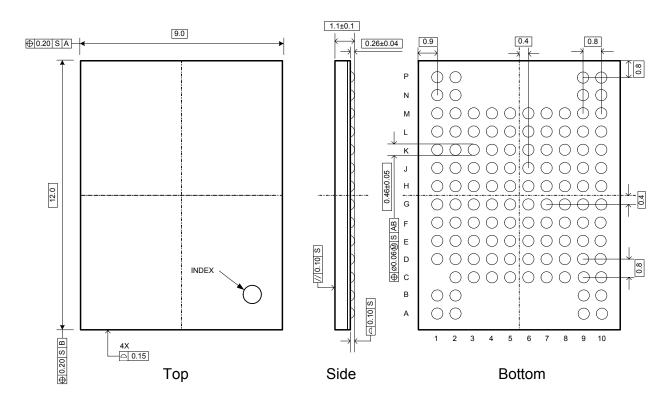

## 6. MECHANICAL DIMENSIONS

#### mDOC H3 1Gb (128MB) / 2Gb (256MB)

FBGA 128MB (1Gb) dimensions:  $9.0 \pm 0.20 \text{ mm x } 12.0 \pm 0.20 \text{ mm x } 1.1 \pm 0.1 \text{ mm}$

Figure 7: Mechanical Dimensions 9x12 FBGA Package

# 7. SOFTWARE CHANGES

- The software version must be upgraded to TrueFFS 7.1 for mDOC H3 devices. TrueFFS 7.1 supports both mDOC G3/P3, G3/P3 LP, G4, H1 and H3 families

- Boot code must be changed to support the new product line of mDOC H3. This includes:

- o Initiation Program Loader (IPL)

- o Secondary Program Loader (SPL) not needed in mDOC H3

- o Rebuild of O/S Boot loader.

- More information regarding TrueFFS 7.x can be found in:

- o mDOC TrueFFS 7.1 Software Development Kit (SDK) developer guide.

- o mDOC Software Utilities for TrueFFS 7.1 user manual.

## 8. Additional Information

Additional information about mDOC product families, including data sheets, developer guide and application notes, can be found at <a href="https://www.m-systems.com">www.m-systems.com</a>.

| Document        | Description                                          |

|-----------------|------------------------------------------------------|

| Data Sheet      | mDOC G4 128MB/1Gb, 256MB/2Gb                         |

| Data Sheet      | mDOC H1 512MB/4Gb, 1GB/8Gb                           |

| Data Sheet      | mDOC H1 256MB/2Gb                                    |

| Data Sheet      | mDOC H3                                              |

| Developer Guide | mDOC TrueFFS 7.1 Software Developer Kit (SDK)        |

| Developer Guide | mDOC TrueFFS 7.1 Boot Software Development Kit (BDK) |

| Developer Guide | mDOC TrueFFS 7.1 Software Utilities                  |

| Developer Guide | mDOC Driver Extended Functions Based on TrueFFS 7.1  |

### How to Contact Us

#### **USA**

M-Systems, Inc.

555 North Mathilda Avenue, Suite 220

Sunnyvale, CA 94085 Phone: +1-408-470-4440 Fax: +1-408-470-4470

#### Japan

M-Systems Japan Inc.

Asahi Seimei Gotanda Bldg., 3F

5-25-16 Higashi-Gotanda

Shinagawa-ku Tokyo, 141-0022

Phone: +81-3-5423-8101 Fax: +81-3-5423-8102

#### **Taiwan**

M-Systems Asia Ltd. 14 F, No. 6, Sec. 3 Minquan East Road Taipei, Taiwan, 104 Tel: +886-2-2515-2522

Fax: +886-2-2515-2295

#### China

M-Systems China Ltd.

Room 121-122

Bldg. 2, International Commerce & Exhibition Ctr.

Hong Hua Rd.

Futian Free Trade Zone

Shenzhen, China

Phone: +86-755-8348-5218 Fax: +86-755-8348-5418

#### Europe

M-Systems Ltd. 7 Atir Yeda St.

Kfar Saba 44425, Israel Tel: +972-9-764-5000 Fax: +972-3-548-8666

#### Internet

http://www.m-systems.com/mobile

#### **General Information**

info@m-systems.com

#### **Sales and Technical Information**

techsupport@m-systems.com

This document is for information use only and is subject to change without prior notice. Msystems Flash Disk Pioneers Ltd. assumes no responsibility for any errors that may appear in this document. No part of this document may be reproduced, transmitted, transcribed, stored in a retrievable manner or translated into any language or computer language, in any form or by any means, electronic, mechanical, magnetic, optical, chemical, manual or otherwise, without prior written consent of Msystems.

Msystems products are not warranted to operate without failure. Accordingly, in any use of the Product in life support systems or other applications where failure could cause injury or loss of life, the Product should only be incorporated in systems designed with appropriate and sufficient redundancy or backup features.

Contact your local Msystems sales office or distributor, or visit our website at <a href="www.msystems.com">www.msystems.com</a> to obtain the latest specifications before placing your order.

© 2006 Msystems Flash Disk Pioneers Ltd. All rights reserved.

Msystems, DiskOnChip, DiskOnChip Millennium, DiskOnKey, DiskOnKey MyKey, FFD, Fly-By, iDiskOnChip, iDOC, mDiskOnChip, mDOC, Mobile DiskOnChip, Smart DiskOnKey, SmartCaps, SuperMAP, TrueFFS, uDiskOnChip, uDOC, and Xkey are trademarks or registered trademarks of M Systems Flash Disk Pioneers, Ltd. Other product names or service marks mentioned herein may be trademarks or registered trademarks of their respective owners and are hereby acknowledged. All specifications are subject to change without prior notice.