# **Quad Input Redundant IDCS Clock Generator**

The MPC9894 is a differential input and output, PLL-based Intelligent Dynamic Clock Switch (IDCS) and clock generator specifically designed for redundant clock distribution systems. The device receives up to four LVPECL clock signals and generates eight phase-aligned output clocks. The MPC9894 is able to detect failing clock signals and to dynamically switch to a redundant clock signal. The switch from the failing clock to the redundant clock occurs without interruption of the output clock signal (output clock slews to alignment). The phase bump typically caused by a clock failure is eliminated. The device offers eight low-skew clock outputs organized into four output banks, each configurable to support the different clock frequencies. The extended temperature range of the MPC9894 supports telecommunication and networking requirements.

#### **Features**

- 8 differential LVPECL output pairs

- · Quad-redundancy reference clock inputs

- IDCS-on-chip intelligent dynamic clock switch

- Smooth output phase transition during clock failover switch/\*

- Automatically detects clock failures

- · Clock activity monitor

- Clock qualifier inputs

- · Manual clock select and automatic switch modes

- 21.25 340 MHz output frequency range

- · Specified frequency and phase slew rate on clock switch

- LVCMOS compatible control inputs and outputs

- External feedback enables zero-delay configurations

- Output enable/disable and static test mode (PLL bypass)

- Low-skew characteristics: maximum 50 ps<sup>(1)</sup> output-to-output

- I<sup>2</sup>C interface for device configuration

- · Low cycle-to-cycle and period jitter

- IEEE 1149.1 JTAG Interface

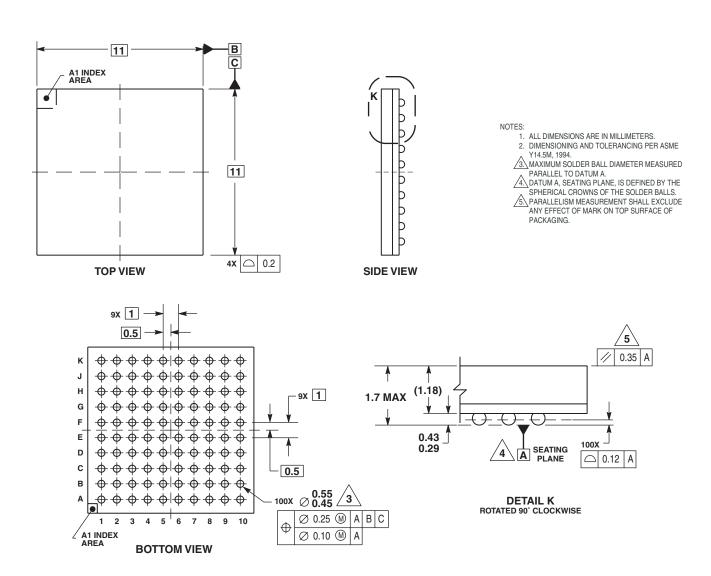

- 100-ball MAPBGA package

- Supports 2.5 V or 3.3 V supplies with 2.5 V and 3.3 V I/O

- Junction temperature range –40°C to +110°C

# **Functional Description**

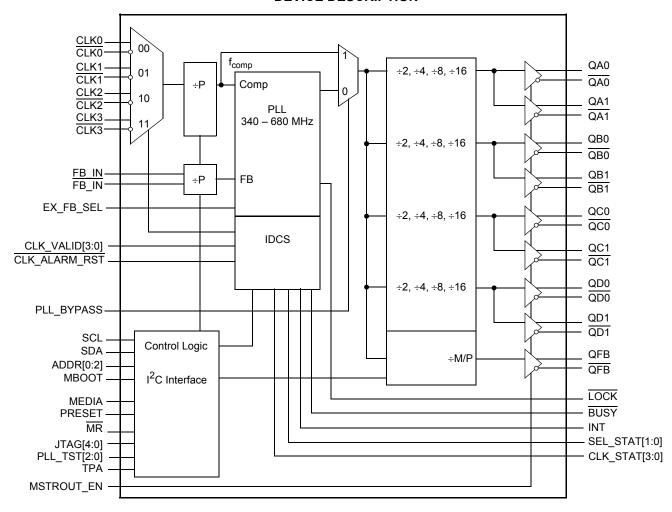

The MPC9894 is a quad differential redundant input clock generator. The device contains logic for clock failure detection and auto switching for clock redundant applications. The generator uses a fully integrated PLL to generate clock signals from any one of four redundant clock sources. The PLL multiplies the frequency of the input reference clock by one, two, four, eight or divides the reference clock by two or four. The frequency-multiplied clock signal drives four banks of two differential outputs. Each bank allows an individual frequency-divider configuration. All outputs are phase-aligned<sup>(1)</sup> to each other. Due to the external PLL feedback, the clock signals of all outputs are also phase-aligned<sup>(1)</sup> to the selected input reference clock, providing virtually zero-delay capability.

The integrated IDCS continuously monitors all four clock inputs and indicates a clock failure for each clock input. When a false clock signal is detected on the active clock, the MPC9894 switches to a redundant clock input, forcing the PLL to slowly slew to alignment and not produce any phase bumps at the outputs. The MPC9894 also provides a manual mode that allows for user-controlled clock switches.

The device is packaged in a 11x11 mm<sup>2</sup> 100-ball MAPBGA package.

1. At coincident rising edges.

# MPC9894

QUAD INPUT REDUNDANT IDCS CLOCK GENERATOR

VF SUFFIX 100-LEAD MAPBGA PACKAGE CASE 1462-01

# **DEVICE DESCRIPTION**

Figure 1. MPC9894 Block Diagram

**Table 1. Pin Configurations**

| Pin                                                  | I/O    | Type   | Function                                                                                                                                          | Supply            | Active State |

|------------------------------------------------------|--------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|--------------|

| Clock Inputs and O                                   | utputs |        |                                                                                                                                                   |                   | •            |

| CLK0, CLK0<br>CLK1, CLK1<br>CLK2, CLK2<br>CLK3, CLK3 | Input  | LVPECL | PLL reference clock inputs (differential) (internal pulldown)                                                                                     | V <sub>DDIC</sub> | _            |

| FB_IN, FB_IN                                         | Input  | LVPECL | PLL feedback signal input (differential). When configured for external feedback, the QFB output should be connected to FB_IN. (internal pulldown) | V <sub>DDIC</sub> | _            |

| QA[1:0], QA[1:0]                                     | Output | LVPECL | Bank A differential outputs                                                                                                                       | $V_{DDAB}$        | _            |

| QB[1:0], QB[1:0]                                     | Output | LVPECL | Bank B differential outputs                                                                                                                       | $V_{DDAB}$        | _            |

| QC[1:0], QC[1:0]                                     | Output | LVPECL | Bank C differential outputs                                                                                                                       | $V_{DDCD}$        | _            |

| QD[1:0], QD[1:0]                                     | Output | LVPECL | Bank D differential outputs                                                                                                                       | $V_{DDCD}$        | _            |

| QFB, QFB                                             | Output | LVPECL | Differential PLL feedback output. QFB must be connected to FB_IN for correct operation                                                            | V <sub>DDCD</sub> | _            |

**Table 1. Pin Configurations (Continued)**

| Pin                           | I/O     | Туре   | Function                                                                                                           |                   | Active State |

|-------------------------------|---------|--------|--------------------------------------------------------------------------------------------------------------------|-------------------|--------------|

| Control Inputs and            | Outputs |        |                                                                                                                    |                   | •            |

| EX_FB_SEL                     | Input   | LVCMOS | Selects between external feedback and internal feedback                                                            | V <sub>DD</sub>   | high         |

| CLK_VALID[3:0] <sup>(1)</sup> | Input   | LVCMOS | Validates the clock inputs CLK0 to CLK3 (internal pullup)                                                          | $V_{DD}$          | high         |

| CLK_ALARM_RST                 | Input   | LVCMOS | Reset of all four alarm status flags and clock selection status flag (internal pullup)                             | $V_{DD}$          | low          |

| PLL_BYPASS                    | Input   | LVCMOS | Select static test mode (internal pulldown)                                                                        | $V_{DD}$          | high         |

| MEDIA                         | Input   | LVCMOS | Output impedance control                                                                                           | $V_{DD}$          | high         |

| MR                            | Input   | LVCMOS | Device reset (internal pullup)                                                                                     | $V_{DD}$          | low          |

| LOCK                          | Output  | LVCMOS | PLL lock indicator                                                                                                 | $V_{DD}$          | low          |

| CLK_STAT[3:0]                 | Output  | LVCMOS | Clock input status indicator                                                                                       | $V_{DD}$          | high         |

| SEL_STAT[1:0]                 | Output  | LVCMOS | Reference clock selection indicator                                                                                | $V_{DD}$          | high         |

| BUSY                          | Output  | LVCMOS | IDCS switching activity indicator                                                                                  | $V_{DD}$          | low          |

| MBOOT                         | Input   | LVCMOS | Activates I <sup>2</sup> C boot sequence (internal pulldown)                                                       | $V_{DD}$          | high         |

| PRESET                        | Input   | LVCMOS | Enables Preset configuration of configuration registers on release of MR (internal pulldown)                       | $V_{DD}$          | high         |

| ĪNT                           | Output  | OD     | Indicate any status IDCS change                                                                                    | V <sub>DD</sub>   | low          |

| MSTROUT_EN                    | Input   | LVCMOS | Master Enable for all Outputs (internal pulldown)                                                                  |                   | high         |

| SEL_2P5V                      | Input   | LVCMOS | Device core power supply selection for VDD and VDDA                                                                | V <sub>DD</sub>   | high         |

| I <sup>2</sup> C Interface    | ı       |        | -                                                                                                                  |                   |              |

| SCL                           | I/O     | OD     | <sup>2</sup> C interface control, clock                                                                            |                   | _            |

| SDA                           | I/O     | OD     | <sup>2</sup> C interface control, data                                                                             |                   | _            |

| ADDR[2:0]                     | Input   | LVCMOS | 1 <sup>2</sup> C interface address lines (10K pullup)                                                              |                   | high         |

| IEEE 1149.1 and Te            | st      |        |                                                                                                                    |                   | •            |

| TMS                           | Input   | LVCMOS | JTAG test mode select (10K pullup)                                                                                 | $V_{DDIC}$        | _            |

| TDI                           | Input   | LVCMOS | JTAG test data input (10K pullup)                                                                                  | $V_{DDIC}$        | _            |

| TDO                           | Output  | LVCMOS | JTAG test data output                                                                                              | $V_{DDIC}$        | _            |

| TCK                           | Input   | LVCMOS | JTAG test clock                                                                                                    | V <sub>DDIC</sub> | _            |

| TRST                          | Input   | LVCMOS | JTAG test reset (10K pullup)                                                                                       | V <sub>DDIC</sub> | _            |

| PLL_TEST[2:0]                 | Input   | LVCMOS | PLL_TEST pins (factory use only, MUST BE CONNECTED TO GND)                                                         | N/A               | _            |

| TPA                           | Output  | LVCMOS | PLL Analog test pin (factory use only, LEAVE OPEN)                                                                 | $V_{DDA}$         | _            |

| Power and Ground              | ı       |        | -                                                                                                                  |                   |              |

| GND                           | Supply  | Ground | Negative power supply                                                                                              | _                 | _            |

| $V_{DD}$                      | Supply  | _      | Positive power supply for the device core, output status and control inputs. (3.3 V or 2.5 V)                      | _                 | _            |

| $V_{DDAB}$                    | Supply  | _      | Supply voltage for output banks A and B (QA0 through QB1) (3.3 V or 2.5 V)                                         |                   | _            |

| $V_{DDCD}$                    | Supply  | _      | Supply voltage for output banks C and D (QC0 through QD1) and QFB (3.3 V or 2.5 V)                                 |                   | _            |

| V <sub>DDIC</sub>             | Supply  | _      | Supply voltage for differential inputs clock inputs CLK0 to CLK3 and FB_IN (3.3 V or 2.5 V)                        | _                 |              |

| $V_{DDA}$                     | Supply  | _      | Clean supply for analog portions of the PLL (This voltage is derived via a RC filter from the $\rm V_{DD}$ supply) | _                 | _            |

<sup>1.</sup> bit order = msb to lsb.

**Table 2. Function Table**

| Control             | Default | 0                                                                                                                                                                                                                                                                               | 1                                                                                                                                                                                                                             |

|---------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Control Inputs      |         |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                               |

| PLL_BYPASS          | 0       | PLL enabled. The input to output frequency relationship is according to Table 9 if the PLL is frequency locked.                                                                                                                                                                 | PLL bypassed and IDCS disabled. The VCO output is replaced by the reference clock signal f <sub>REF</sub> . This is considered to be a test mode and clock monitoring and clock switching are disabled during this operation. |

| CLK_VALID[3:0]      | 0       | The associated clock input is considered to be invalid and usable                                                                                                                                                                                                               | The associated clock input is considered to be a valid usable clock input                                                                                                                                                     |

| CLK_ALARM_RST       | 1       | CLK_STAT[3:0] and SEL_STAT[1:0] flags are reset: CLK_STAT[3:0] = 0000 and SEL_STAT[1:0] = 00. CLK_ALARM_RST is a one-shot function.                                                                                                                                             | CLK_STAT[3:0] and SEL_STAT[1:0] flags are active                                                                                                                                                                              |

| MR                  | 1       | Reset of data generators and output dividers. The MPC9894 requires reset at power-up and after any loss of PLL lock. Loss of PLL lock may occur when the external feedback path is interrupted. The length of the reset pulse should be greater than two reference clock cycles | Outputs enabled (active)                                                                                                                                                                                                      |

| MBOOT               | 0       | I <sup>2</sup> C read/write mode                                                                                                                                                                                                                                                | I <sup>2</sup> C boot mode                                                                                                                                                                                                    |

| PRESET              | 0       | Normal Operation                                                                                                                                                                                                                                                                | Uses Configuration Register PRESET values on MR                                                                                                                                                                               |

| EX_FB_SEL           | 0       | Selects internal feedback path                                                                                                                                                                                                                                                  | Selects external feedback path                                                                                                                                                                                                |

| MEDIA               | 0       | Low output impedance (QA0 to QD1 and QFB)                                                                                                                                                                                                                                       | 50 $\Omega$ output impedance (QA0 to QD1 and QFB)                                                                                                                                                                             |

| SEL_2P5V            | 0       | Selects 3.3 V for core V <sub>DD</sub>                                                                                                                                                                                                                                          | Selects 2.5 V for core V <sub>DD</sub>                                                                                                                                                                                        |

| MSTROUT_EN          |         | All outputs disabled (synchronous with clock being low)                                                                                                                                                                                                                         | All outputs enabled                                                                                                                                                                                                           |

| Control Outputs     |         |                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                               |

| LOCK <sup>(1)</sup> |         | PLL is locked                                                                                                                                                                                                                                                                   | PLL is unlocked                                                                                                                                                                                                               |

| BUSY <sup>(1)</sup> |         | The IDCS has initiated a clock switch.                                                                                                                                                                                                                                          | No clock switch currently performed                                                                                                                                                                                           |

| ĪNT                 |         | IDCS status has changed (indicates an assertion of CLK_STAT[3:0] or deassertion of LOCK)                                                                                                                                                                                        | No status change                                                                                                                                                                                                              |

| CLK_STAT[3:0]       |         | Associated clock input not valid                                                                                                                                                                                                                                                | Associated clock input valid                                                                                                                                                                                                  |

| SEL_STAT[1:0]       |         | Encoded value refer to Table 7                                                                                                                                                                                                                                                  | Encoded value refer to Table 7                                                                                                                                                                                                |

<sup>1.</sup> The combined pins of  $\overline{\mathsf{LOCK}}$  = 1 and  $\overline{\mathsf{BUSY}}$  = 0 are used to indicate a catastrophic failure. Refer to PLL Out-of-Lock Conditions.

#### **OPERATING INFORMATION**

#### **Basic Functional Description**

The MPC9894 is a quad-redundancy IDCS clock generator. The redundancy feature allows automatic switching from the reference clock source to a secondary clock source on detection of a failed reference clock. The MPC9894 will detect and report a missing clock on any of its four inputs. Based upon the current IDCS mode setting and the qualifier input pins, the MPC9894 will switch to the next qualified secondary clock.

The input clock sources, CLK0, CLK1, CLK2, and CLK3, are assumed to be the same frequency<sup>(1)</sup> but non-phase-related sources. When a clock switch occurs, the phase alignment to the new clock source will occur over an extended time period, eliminating runt clock output pulses. The maximum rate of phase change is specified in the AC parameter Delta Period per Cycle(<sup>A</sup>PER/CYC). The device uses a fully integrated PLL to generate clock signals from redundant clock sources. The PLL multiplies the input reference clock signal by a variety of values, including 0.25, 0.5, 1, 2, 4 or 8. For a complete list refer to Table 9. The frequency multiplied clock signal drives four independent output banks. Each output bank is phase-aligned to the input reference clock phase, providing virtually zero-delay capability<sup>(2)</sup>.

The configuration of the MPC9894 series of clock generators is performed through either the I<sup>2</sup>C interface or by the preset configuration mode. The I<sup>2</sup>C interface uses a 2 pin interface to transmit clock and data to and from a series of configuration and status registers in the MPC9894.

#### **Definitions**

# IDCS:

Intelligent Dynamic Clock Switch. The IDCS monitors the clock inputs CLK0, CLK1, CLK2, and CLK3. Upon a failure of the reference clock signal, the IDCS switches to a qualified secondary clock signal and the status flags are set.

# Reference clock signal:

The input clock signal that is selected by the IDCS or IDCS MODE[2:0] as the input reference to the PLL.

#### Primary clock:

The input clock signal selected by IDCS\_MODE[2:0]. The primary clock may or may not be the reference clock, depending on IDCS mode and IDCS status.

#### Secondary clock:

The input clock signal which will be selected by the IDCS upon an automatic clock switch.

#### Tertiary, Quaternary clocks:

The input clock signals that will be selected by the IDCS, in turn, after the current secondary clock. This clock selection is based upon a round robin rotational sequence

#### Manual IDCS mode:

The reference clock input is selected by IDCS\_MODE[0xx].

#### Automatic IDCS mode:

The reference clock signal is determined by the IDCS.

#### Selected clock:

The SEL\_STAT[1:0] flags indicate the reference clock signal.

# Qualified clock:

The corresponding CLK\_VALID[3:0] signal is logic high, the associated CLK\_STAT status bit is logic high and no clock failure is present.

#### Bit Orderina:

The bit ordering convention used in this document for both pin and register documentation is NAME[7:0] where bit 7 is the most significant bit and 0 is the least significant bit.

<sup>1.</sup> Refer to Table 39 for clock frequency specification.

<sup>2.</sup> Using external feedback.

#### **DEVICE CONFIGURATION**

# I<sup>2</sup>C Configuration and I<sup>2</sup>C Addressing

The MPC9894 is configured via a series of 8-bit registers. The bits in these registers allow a wide range of control over the operation of the MPC9894 clock generator. These registers are accessed via an I<sup>2</sup>C interface through which a 7-bit address is sent from the I<sup>2</sup>C master to select the specific I<sup>2</sup>C slave device being accessed. The address for this clock driver is found in the first of the MPC9894 I2C registers. The format of this address has a fixed most-significant four bits of binary 1101 while the least-significant 3 address bits are read from the 3 ADDR pins. This provides the capability to configure up to 8 clock devices on a single I<sup>2</sup>C interface.

In addition, activation of the MBOOT pin on power-up or reset initiates an automatic boot sequence allowing the clock generators to be initialized from an I<sup>2</sup>C compatible EEPROM. In this case the MPC9894 becomes an I<sup>2</sup>C master and the

configuration bits are filled by the information from the first 6 bytes of the EEPROM. This allows the clock to be configured without a controlling  $I^2C$  bus master if desired. The PRESET pin allows the device to be configured without a  $I^2C$  bus master.

The detailed register descriptions are found in the section, I<sup>2</sup>C Interface and configuration/status register.

#### **IDCS MODE Configuration**

Three register bits are used to configure the MPC9894 in either an automatic clock switch mode or into a manual clock select mode. The three mode select bits are defined in Table 3.

IDCS modes 000 through 011 allow manual selection between the four clock sources. IDCS modes 100 through 111 enable the automatic mode of the IDCS.

Table 3. MPC9894 IDCS Configuration

| IDCS_MODE [2:0] | Description | Primary Clock | Secondary Clock <sup>(1)</sup> | Tertiary Clock | Quaternary Clock |

|-----------------|-------------|---------------|--------------------------------|----------------|------------------|

| 000             | Manual      | CLK0          | n/a                            | n/a            | n/a              |

| 001             |             | CLK1          | n/a                            | n/a            | n/a              |

| 010             |             | CLK2          | n/a                            | n/a            | n/a              |

| 011             |             | CLK3          | n/a                            | n/a            | n/a              |

| 100             | Automatic   | CLK0          | CLK1                           | CLK2           | CLK3             |

| 101             |             | CLK1          | CLK2                           | CLK3           | CLK0             |

| 110             |             | CLK2          | CLK3                           | CLK0           | CLK1             |

| 111             |             | CLK3          | CLK0                           | CLK1           | CLK2             |

<sup>1.</sup> For CLK\_VALID[3:0] = 1111 and input clock validity.

#### **Automatic IDCS Mode**

In the automatic mode, the clock failure detection is enabled and the IDCS overwrites the selected clock on a clock failure. The IDCS operation requires PLL\_BYPASS = 0 and IDCS\_MODE[2] = 1. The reference clock is handled in a round robin method based upon clock validity and the qualification input CLK\_VALID[3:0]: The qualification input is obtained from the four input pins, CLK\_VALID[3:0]. If any of the CLK\_VALID pins are low the associated clock input will be considered "unqualified" and thus not selected as a reference clock. Alternatively, if a clock input does not have a valid clock signal, it will not be selected and the next qualified and valid clock is selected as the reference clock.

For example, if IDCS\_MODE[2:0] = 100 (the IDCS is in automatic mode), CLK\_VALID[3:0] = 1111 and CLK0, CLK1, CLK2, and CLK3 have valid input clock signals then CLK0 is the primary clock and CLK1 is the secondary clock. The IDCS selects the primary clock as the reference clock and the PLL will phase-lock the clock outputs to the CLK0 input. Upon the failure of CLK0 the IDCS will select CLK1 as the reference clock and initiate a switch, making CLK1 the reference clock and CLK2 the secondary clock. If CLK1 fails, the IDCS will switch to CLK2, etc.

A de-asserted CLK\_VALID[] pin disables the associated clock input as secondary clock. The associated clock input cannot be selected by the IDCS as secondary clock signal. For instance, if CLK0 is the primary clock and

An invalid clock<sup>(1)</sup> signal triggers the associated clock status output (CLK\_STAT[3:0]), independent of the primary and reference clock. These <u>pins go set on a clock</u> failure and remain set (sticky) until the CLK\_ALARM\_RST pin or the individual alarm reset bits (ALARM\_RST[3:0]) are asserted. The CLK\_STAT[3:0] outputs are mirrored in the device register 4 for I<sup>2</sup>C bus access.

After each successful IDCS-commanded switch, the primary clock as set by IDCS\_MODE[1xx] is no longer the reference clock. The user may reset the IDCS flags by asserting the individual ALARM\_RST[3:0] bits after each IDCS-commanded switch. Activation of ALARM\_RST[3:0] does not change the reference clock. A user-commanded change of the primary clock in automatic mode requires a write command to the IDCS\_MODE[2:0] = 0xx bits (the primary clock and SEL\_STAT[1:0] can be freely changed by setting IDCS\_MODE[2:0] = 1xx). If the reference clock is not the primary clock, a write command to IDCS\_MODE[2:0] = 1xx will cause the PLL to lock on the primary clock, given the new primary clock is a qualified clock.

CLK\_VALID[3:0] = 1101, the IDCS will select CLK2 upon a clock failure of CLK0 (CLK1 is disabled by the CLK\_VALID1 input, allowing external logic to control the IDCS switch logic). If a clock is the reference clock signal and its associated CLK\_VALID signal is switched from 'valid' to 'invalid', the IDCS initiates a clock input switch, selecting the next available clock input (secondary clock).

<sup>1.</sup> See Clock Failure Detection.

Table 4. Input Clock Qualifier and Status Flag

| Input Clock |                                           |           | nput Clock Status Flag   |

|-------------|-------------------------------------------|-----------|--------------------------|

| input Clock | Associated Input Qualifier <sup>(1)</sup> | Pin       | Register location        |

| CLK0        | CLK_VALID0                                | CLK_STAT0 | Device register 5, bit 3 |

| CLK1        | CLK_VALID1                                | CLK_STAT1 | Device register 5, bit 4 |

| CLK2        | CLK_VALID2                                | CLK_STAT2 | Device register 5, bit 5 |

| CLK3        | CLK_VALID3                                | CLK_STAT3 | Device register 5, bit 6 |

<sup>1.</sup> The input qualifier logic can be enabled or disabled by setting the QUAL\_EN bit in register 3.

#### Table 5. Input Clock Status CLK STAT[3:0]

| CLK_STAT[] | Description              |

|------------|--------------------------|

| 0          | Clock input failure      |

| 1          | Clock input signal valid |

#### Table 6. Clock Input Qualifier CLK\_VALID[3:0]

| CLK_VALID[] | Associated Input Clock                 |  |  |

|-------------|----------------------------------------|--|--|

| 0           | Not qualified and will not be selected |  |  |

| 1           | Qualified                              |  |  |

The SEL\_STAT[1:0] pins indicate which of the four input clocks is the current reference clock. In the automatic mode and In the case of the reference clock failure, the SEL\_STAT

flag will indicate a reference clock different from the original primary clock selected by IDCS\_MODE[2:0]. The CLK\_STAT outputs are mirrored in register 5, bits 1:0 for I<sup>2</sup>C bus access.

Table 7. SEL\_STAT[1:0]

| SEL_STAT[1:0] | Selected clock input |

|---------------|----------------------|

| 00            | CLK0                 |

| 01            | CLK1                 |

| 10            | CLK2                 |

| 11            | CLK3                 |

If all four clock inputs are not qualified the VCO will slew to its lowest frequency. This condition will be indicated by the LOCK pin being de-asserted. The MPC9894 will remain in this state until an input clock is restored and the device is reset via the  $\overline{\text{MR}}$  pin.

#### **Clock Failure Detection**

The MPC9894 clock failure detection is performed using an input clock amplitude check combined with an activity detector. The following conditions will trigger a failed clock status (CLK\_STATn = 0) on any qualified clock (CLK\_VALIDn = 1). These conditions are:

- 1. Either or both CLKx, CLKx are disconnected from the input clock source and open.

- 2. CLKx and CLKx are shorted together

- 3. Either or both CLKx or CLKx are shorted to GND

- 4. Both CLKx and CLKx are shorted to a power supply

- Amplitude of CLKx or CLKx is less than V<sub>PP, OK</sub> (refer to AC specification, Table 39)

In addition, the currently selected clock is checked by a phase-frequency detector after the input divider (P). This is

triggered by a phase step of  $mae_{(\emptyset)}$ . This phase detector will issue a failed clock status (CLK\_STATn = 0) within 'P' clock cycles.

The IDCS does not detect changes of the reference frequency or the reference frequency being out of the specified input frequency range. This includes errors such as reference frequency drift due to crystal aging etc.

### **Clearing of IDCS Alarm Flags**

The input clock status flags are set by a clock failure and remain set until manually cleared (sticky). Clearing can be done by either of two methods. All status flags can be cleared by the package pin, CLK\_ALARM\_RST. Or individual status flags can be cleared via register bits, ALARM\_RST[3:0]. The CLK\_ALARM\_RST pin is activated by a negative edge on the pin. This clears all CLK\_STAT[3:0] flags and returns the IDCS to the primary clock source. The SEL\_STAT[1:0]-selected clock indicator now reflects the IDCS MODE[2:0] setting.

By using ALARM\_RST[3:0] (register 2) individual CLK\_STAT[3:0] bits are cleared by writing a logic 0 to the individual bit in this register. It is important to note that this action does not return the IDCS to the primary clock.

#### **IDCS Manual Mode**

The manual request IDCS mode is selected by IDCS\_MODE[2:0] = 0xx. The PLL functions normally and all four inputs clocks are monitored. The reference clock will always be the clock signal selected by IDCS\_MODE[1:0] and will be indicated by SEL\_STAT[1:0]. A manual-requested clock switch (by changing the IDCS\_MODE[0xx] signal) will only be executed if the new clock is valid. The SEL\_STAT[1:0] pins/bits should be checked after the manual request to ensure the clock switch occurred.

#### **Interrupt Operation**

The MPC9894 pin,  $\overline{\text{INT}}$ , may be used to interrupt a microprocessor or microcontroller. This open drain output pin goes active or low on any of the following occurrences

- A clock failure as indicated by any of bits 6 thru 3 being set in the status register

- A out-of-lock condition for the PLL as indicated by either the LOCK pin or bit 2 of the status register.

The interrupted processor would then use the I<sup>2</sup>C interface to read the status register (bit 7) to determine if this MPC9894 generated the interrupt. If the interrupt was caused by this MC9894, the status register would then be analyzed to determine the reason for the interrupt and then the appropriate action taken.

In order for interrupts to occur, the INT\_E bit must be set in the Device Configuration and Output Clock Enable Register. Once the interrupt flag has been set, reading of the Status Register clears the INT flag.

#### **Clock Operation on Power-Up**

On or after power-up, the MPC9894 must be reset via the  $\overline{\text{MR}}$  pin. The MPC9894 may be powered-up in either of three configurations. These configurations are selected by the PRESET pin and MBOOT pin.

If PRESET is low, on release of the  $\overline{\text{MR}}$  pin, the MPC9894 powers up in a benign mode with all clock outputs disabled. The device is ready to be and must be programmed via the I<sup>2</sup>C interface prior to operation.

If the PRESET pin is high on the release of the  $\overline{\text{MR}}$  pin, the MPC9894 powers up in a run state. In this case the IDCS is configured for automatic mode, CLK0 to be the primary clock, a divide by 2 on clock bank A and B outputs, a divide by 8 on clock C and D outputs, all clock output banks enabled and interrupts enabled. If using the preset mode, then at least one of the clock inputs must have the correct input frequency prior to  $\overline{\text{MR}}$  going high.

Later in this document, tables defining the  $I^2C$  interface registers describe both configurations. The default (reset) information is for the normal reset operation, while the default (preset) information describes the values for each configuration bit on activation of the PRESET pin. In order to return the MPC9894 to either the preset or reset configuration the  $\overline{MR}$  pin must be activated.

Refer to the Boot Mode for a description of the MBOOT pin.

#### **PLL Feedback**

The MPC9894 may be operated with either an internal or an external PLL feedback path. The selection of internal vs. external feedback is made with the pin, EX\_FB\_SEL. If external feedback is desired, the EX\_FB\_SEL pin should be connected to V\_DD and a connection from QFB/QFB to FB\_IN/FB\_IN must be made. External feedback provides a known relationship between the clock input and the feedback input for phase synchronization of output clock signals to the clock input. If this phase synchronization is not required, the MPC9894 may be configured for internal feedback by the connection of EX\_FB\_SEL to ground. In this configuration, the connection from the feedback output to the feedback input is not required. The feedback output may be used as a separate output to produce a reference clock output.

#### **PLL Out-of-Lock Conditions**

The  $\overline{\text{LOCK}}$  pin and associated status bit indicates the lock state of the PLL. After power-up and prior to writing configuration data to the control registers, an out-of-lock condition will be indicated by  $\overline{\text{LOCK}}$  = 1. If a valid clock is available and proper configuration data is written to the control registers,  $\overline{\text{LOCK}}$  will then indicate the PLL is in a locked condition with  $\overline{\text{LOCK}}$  = 0.

The combination of  $\overline{LOCK}$  = 1 and  $\overline{BUSY}$  = 0 is used to indicate a catastrophic failure of the PLL. This condition will occur on the following:

- 1. All input clocks have failed or no clock is present.

- External feedback has been selected with the EX\_FB\_SEL pin and an external feedback signal is not present on the FB\_IN/FB\_IN inputs. It should be noted that if this condition occurs during the initial PLL lock acquisition the PLL will produce a clock that is locked to the internal feedback path. However, the catastrophic failure status of LOCK = 1 and BUSY = 0 will occur.

Recovery from the catastrophic failure condition requires repairing the cause of the failure, followed by a master reset to be issued to the MPC9894.

#### **CLOCK OUTPUT TRANSITION**

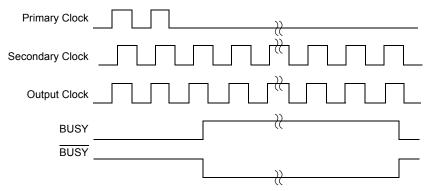

An MPC9894 clock switch, either in IDCS manual or IDCS automatic mode, follows the next positive edge of the newly selected reference clock signal. The positive edge of the feedback clock and the newly selected reference clock edge will start to slew to alignment by adjusting the feedback edge placement a small amount of time in each clock cycle. Figure 2. Clock Switch shows a failed primary input clock with the MPC9894 switching to and aligning to the secondary clock. This small amount of additional time in each clock cycle will ensure that the output clock does not have any large phase changes or frequency changes in a short period of time. The alignment will be to either 1) the closest edge,

either forward or backward or 2) toward the lagging clock edge. The maximum rate of period change is specified in the AC parameter tables with the parameter of  $^{\Delta}_{\rm PER/CYC}.$  This parameter implies that the output clock edge will never change more than the specified amount in any one cycle.

The busy signal is used to indicate that the MPC9894 is in the process of slewing to the new input clock alignment. The signal is accessed thru the BUSY pin and goes set upon a clock switch. The pin is reset once the phase realignment is completed. During the period that BUSY is active, the configuration register of the MPC9894 should not be written with new configuration data.

Figure 2. Clock Switch

For example, if the current input clock of 62.5 MHz and the secondary clock are 180 degrees out of phase then the minimum clock transition time can be calculated by

$$t_{cycle} = 1 \div f_{cycle} = 1 \div 62.5 \text{ MHz} = 16 \text{ ns}$$

Therefore 180 degree clock difference is

$$t_{cycle} \div 2 = 8 ns$$

Assuming a  $^{\Delta}_{PER/CYC}$  of 40 ps, then

This is the minimum number of cycles that will be required for the alignment to the new clock. The alignment to the new clock phase may occur slower than this but never faster.

The alignment on clock failure is selectable between either 1) the closest edge, either forward or backward or 2) toward the lagging clock edge. The selection of the alignment method is selected in the Slew\_Control bit (bit 5) of the Device Configuration and Output Enable Register. This selection allows the user to select the alignment method that best suits the application. The characteristics and subsequent advantages and disadvantages of each method are described as follows.

- 1. Slew to closest edge

- The alignment is either forward toward the lagging edge or backward toward the leading edge.

- The alignment to the closest edge ensures re-alignment to the new clock input in the minimum time

- In applications where the input clocks are closely aligned, there is no ambiguity on the direction of clock slew.

- The clock output frequency will either increase or decrease based on direction of clock slew.

- 2. Slew to lagging edge

- a. The output frequency always decreases. Thus the clock frequency never violates a maximum frequency specification in the user system.

- b. When input clocks are closely aligned (within SPO + jitter) the MPC9894 may align to the closest edge or to the lagging edge. In the case of multiple MPC9894s with equivalent clock inputs one MPC9894 may align in one direction while an other MPC9894 may align to the opposite direction.

If default values for the Slew\_Control is not the configuration desired then the reconfiguration of the slew method should be perform soon after power-up and the configuration should remain fixed from that point.

#### INPUT AND OUTPUT FREQUENCY CONFIGURATION

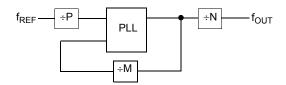

Configuring the MPC9894 input and output frequencies requires programming the internal PLL input, feedback and output dividers. The output frequency is represented by the following formula:

$$f_{OUT} = [(f_{REF} \div P) \cdot M] \div N$$

where  $f_{REF}$  is the reference frequency of the selected input clock source (reference input), M is the PLL feedback divider and N is an output divider. The PLL input divider P, the feedback divider M and the output divider are configured by the device registers 1 and 4. The MPC9894 has four output

banks (Bank A, B, C, and D) and each output bank can be configured individually as shown in Table 8.

Figure 3. PLL Frequency Calculation

Table 8. Configuration of PLL P, M and N Frequency Dividers

| Divider                                      | Available Values   | Configuration Through                  |  |

|----------------------------------------------|--------------------|----------------------------------------|--|

| PLL Input Divider (P)                        | ÷1, ÷2, ÷3, ÷4, ÷6 | Input_FB_Div[3:0], Register 4, bit 3:0 |  |

| PLL Feedback Divider (M)                     | ÷8, ÷12, ÷16       |                                        |  |

| PLL Output Divider, Bank A (N <sub>A</sub> ) | ÷2, ÷4, ÷8, ÷16    | FSEL_B[1:0], Register 1, bit 7:6       |  |

| PLL Output Divider, Bank B (N <sub>B</sub> ) | ÷2, ÷4, ÷8, ÷16    | FSEL_B[1:0], Register 1, bit 5:4       |  |

| PLL Output Divider, Bank C (N <sub>C</sub> ) | ÷2, ÷4, ÷8, ÷16    | FSEL_C[1:0], Register 1, bit 3:2       |  |

| PLL Output Divider, Bank D (N <sub>D</sub> ) | ÷2, ÷4, ÷8, ÷16    | FSEL_D[1:0], Register 1, bit 1:0       |  |

The reference frequency  $f_{REF}$  and the selection of the PLL input divider (P) and feedback-divider (M) is limited by the specified VCO frequency range.  $f_{REF}$ , P and M must be configured to match the VCO frequency range of 340 to 680 MHz in order to achieve stable PLL operation:

$$f_{VCO,MIN} \le (f_{REF} \div P \cdot M) \le f_{VCO,MAX}$$

The PLL input divider (P) can be used to situate the VCO in the specified frequency range. The PLL input divider effectively extends the usable input frequency range.

The output frequency for each bank can be derived from the VCO frequency and output divider (N):

$$f_{QA}[1:0] = f_{VCO} \div N_A$$

$f_{OB}[1:0] = f_{VCO} \div N_B$

$$f_{QC}[1:0] = f_{VCO} \div N_C$$

$$f_{QD}[1:0] = f_{VCO} \div N_D$$

Table 9 illustrates the possible input clock frequency configurations of the MPC9894. Note that the VCO lock range is always 340 MHz to 680 MHz, setting lower and upper boundaries for the frequency range of the device.

**Table 9. Input and Output Frequency Ranges**

| Input_FB_Div[3:0]  | Р        | м   | f <sub>REF</sub> range | Output frequence     | cy for any bank A, I  | 3, C or D (FSEL_x)     | and ratio to f <sub>REF</sub> |

|--------------------|----------|-----|------------------------|----------------------|-----------------------|------------------------|-------------------------------|

| IIIput_FB_DIV[3.0] | Г        | IVI | MHz                    | N = 2                | N = 4                 | N = 8                  | N = 16                        |

| 0                  | ÷1       | ÷16 | 21.25 – 42.5           | 8⋅f <sub>REF</sub>   | 4⋅f <sub>REF</sub>    | 2·f <sub>REF</sub>     | f <sub>REF</sub>              |

| 1                  | ÷1       | ÷12 | 28.33 – 56.67          | 6⋅f <sub>REF</sub>   | 3⋅f <sub>REF</sub>    | 1.5⋅f <sub>REF</sub>   | 0.75·f <sub>REF</sub>         |

| 2                  | ÷2       | ÷12 | 56.66 – 113.34         | 3⋅f <sub>REF</sub>   | 1.5⋅f <sub>REF</sub>  | 0.75⋅f <sub>REF</sub>  | 0.375·f <sub>REF</sub>        |

| 3                  | ÷1       | ÷8  | 42.5 – 85.0            | 4⋅f <sub>REF</sub>   | 2⋅f <sub>REF</sub>    | 1.f <sub>REF</sub>     | 0.5⋅f <sub>REF</sub>          |

| 4                  | ÷2       | ÷16 | 42.5 – 85.0            | 4⋅f <sub>REF</sub>   | 2·f <sub>REF</sub>    | 1.f <sub>REF</sub>     | 0.5⋅f <sub>REF</sub>          |

| 5                  | reserved |     |                        |                      |                       |                        |                               |

| 6                  | ÷2       | ÷8  | 85.0 – 170.0           | 2⋅f <sub>REF</sub>   | 1.f <sub>REF</sub>    | 0.5⋅f <sub>REF</sub>   | 0.125⋅f <sub>REF</sub>        |

| 7                  | ÷3       | ÷12 | 85.0 – 170.0           | 2⋅f <sub>REF</sub>   | 1.f <sub>REF</sub>    | 0.5⋅f <sub>REF</sub>   | 0.125⋅f <sub>REF</sub>        |

| 8                  | ÷4       | ÷16 | 85.0 – 170.0           | 2⋅f <sub>REF</sub>   | 1.f <sub>REF</sub>    | 0.5⋅f <sub>REF</sub>   | 0.125·f <sub>REF</sub>        |

| 9                  |          |     |                        | rese                 | erved                 |                        |                               |

| 10                 | ÷4       | ÷12 | 113.32 – 226.64        | 1.5⋅f <sub>REF</sub> | 0.75⋅f <sub>REF</sub> | 0.375⋅f <sub>REF</sub> | 0.1875·f <sub>REF</sub>       |

| 11                 |          |     |                        | rese                 | erved                 |                        |                               |

| 12                 | reserved |     |                        |                      |                       |                        |                               |

| 13                 | reserved |     |                        |                      |                       |                        |                               |

| 14                 | 4        | ÷8  | 170.0 – 340.0          | 1⋅f <sub>REF</sub>   | 0.5⋅f <sub>REF</sub>  | 0.25·f <sub>REF</sub>  | 0.125·f <sub>REF</sub>        |

| 15                 | 6        | ÷12 | 170.0 – 340.0          | 1⋅f <sub>REF</sub>   | 0.5⋅f <sub>REF</sub>  | 0.25·f <sub>REF</sub>  | 0.125·f <sub>REF</sub>        |

# 12C INTERFACE AND CONFIGURATION/STATUS REGISTERS

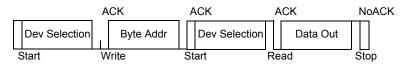

The following tables summarize the bit configurations for the registers accessible via the I<sup>2</sup>C interface. The register values are read or written over the I<sup>2</sup>C interface by the I<sup>2</sup>C Master. This sequence starts with the I<sup>2</sup>C start command, followed by the I<sup>2</sup>C device address and read/write byte. This is then followed by the address of the register that is to be accessed. In the case of a write, the register address byte is followed by the data to be written to that register. In the case

of a read, the device will then respond with the data from that register. At the conclusion of the transfer an  $I^2C$  Stop command is issued by the Master to terminate the transfer. For a complete description of the  $I^2C$  protocol refer to the v2.1  $I^2C$  specification.

Table 10 lists the registers that are accessible via the I<sup>2</sup>C interface.

Table 10. I<sup>2</sup>C Registers

| Address | Register                                                                                  |

|---------|-------------------------------------------------------------------------------------------|

| 0x00    | Table 11. Slave Address (Register 0 — Read Only)                                          |

| 0x01    | Table 12. Output Configuration Register (Register 1 — Read/Write)                         |

| 0x02    | Table 14. Mode Configuration and Alarm Reset Register (Register 2 — Read/Write)           |

| 0x03    | Table 17. Device Configuration and Output Clock Enable Register (Register 3 — Read/Write) |

| 0x04    | Table 22. Input and Feedback Divider Configuration Register (Register 4 — Read/Write)     |

| 0x05    | Table 24. Status Register (Register 5 — Read Only)                                        |

| 0x06    | Table 25. Output Power-Up Register (Register 6 — Read/Write)                              |

| 0x07    | Table 27. Feedback Power-Up Register (Register 7 — Read/Write)                            |

#### **Boot Mode**

When the I<sup>2</sup>C boot mode is activated on power-up or reset via the MBOOT pin, the entire set of writable configuration registers are written with a 6-byte sequence. This sequence starts with the Output Configuration Register, and is followed by the Mode Configuration and Alarm Reset Register, the Device Configuration and Output Clock Enable Register, the Input and Feedback Divider Configuration Register, the Output Power-Up Register and the Feedback Power-Up Register. This equates to the register sequence of 1, 2, 3, 4,

6, 7. This sequence starts with the start command, the device select and read/write(write) byte, followed by the beginning byte address for reading from the EEPROM. This is then followed by the start command, device select and read/write (read) and four current address read bytes. The device address is the binary 7-bit value of 1010000. This I<sup>2</sup>C sequence is compatible with industry standard I<sup>2</sup>C bus EEPROMs such as STMicroelectronics M24C01, or equivalent.

Figure 4. Boot Mode Random Access Read

#### Slave Address Register

The Slave Address register contains the  $I^2C$  address that is used to determine if the data on the  $I^2C$  interface is addressed to this device. The seven-bit address is determined with the fixed value of binary 1101 followed by

variable bits that are obtained from the three address pins. The three input pins allow for 8 different addresses for a given clock generator, allowing up to 8 clock generators to be addressed on a single  $I^2C$  interface.

Table 11. Slave Address (Register 0 — Read Only)

| Bit            | 7        | 6      | 5      | 4      | 3      | 2                                  | 1                                 | 0                                  |

|----------------|----------|--------|--------|--------|--------|------------------------------------|-----------------------------------|------------------------------------|

| Description    | not used | ADDR_6 | ADD_R5 | ADDR_4 | ADDR_3 | ADDR_2<br>read from<br>ADDR[2] pin | ADDR_1<br>read from<br>ADR[1] pin | ADDR_0<br>read from<br>ADDR[0] pin |

| Reset default  |          | 1      | 1      | 0      | 1      |                                    |                                   |                                    |

| Preset default |          | 1      | 1      | 0      | 1      |                                    |                                   |                                    |

#### **Output Configuration Register**

The output configuration register is divided into four, 2 bit-groups with each group selecting the divide ratio for

output banks A through bank D, refer to Table 12. For each bank, four output divider settings ( $\div$ 2,  $\div$ 4,  $\div$ 8,  $\div$ 16) are available, refer to Table 12.

Table 12. Output Configuration Register (Register 1 — Read/Write)

| Bit            | 7    | 6       | 5     | 4       | 3     | 2       | 1     | 0       |

|----------------|------|---------|-------|---------|-------|---------|-------|---------|

| Description    | FSEL | _A[1:0] | FSEL. | _B[1:0] | FSEL. | _C[1:0] | FSEL. | _D[1:0] |

| Reset default  | 0    | 0       | 0     | 0       | 0     | 0       | 0     | 0       |

| Preset default | 0    | 0       | 0     | 0       | 1     | 0       | 1     | 0       |

Table 13. PLL Output Divider N (FSEL\_A to FSEL\_D)

| FSEL_x[1:0] | Value |

|-------------|-------|

| 00          | ÷2    |

| 01          | ÷4    |

| 10          | ÷8    |

| 11          | ÷16   |

#### **Mode Configuration Register**

The mode configuration register, refer to Table 14, is a read/write register and contains the fields for mode selection as well as alarm reset.

The mode of the MPC9894 may be changed by writing the three least significant Mode Configuration Register bits to the desired value. The current idcs mode of the MPC9894 may be obtained by reading this register.

The alarm reset bits, found in bit positions 6 thru 3, may be used to individually reset the status flags of register 5. Each

of these flag bits are associated with the four clock inputs pins and indicate a failed clock input. Clearing of a clock status flag is performed by writing a logic 1 to the individual bit (or bits if more than one flag is to be cleared). Care should be taken to insure that the idcs mode information is written to the proper value when resetting the clock status bits. The four alarm reset bits always read as a logic 0. If a clock input status flag is cleared and the clock input is still in a failed state, the status flag will go set within 4 clock cycles after being cleared.

Table 14. Mode Configuration and Alarm Reset Register (Register 2 — Read/Write)

| Bit            | 7        | 6   | 5                                  | 4   | 3   | 2        | 1                 | 0         |

|----------------|----------|-----|------------------------------------|-----|-----|----------|-------------------|-----------|

| Description    | not used | AL  | ALARM_RST[3:0] (Refer to Table 15) |     |     | IDCS_MOI | DE[2:0] (Refer to | Table 16) |

| Reset default  | n/a      | n/a | n/a                                | n/a | n/a | 0        | 1                 | 1         |

| Preset default | n/a      | n/a | n/a                                | n/a | n/a | 1        | 0                 | 0         |

Table 15. Individual Reset of CLK\_STAT[x] Bits

| ALARM_RST[x] | Description                                                                               |

|--------------|-------------------------------------------------------------------------------------------|

| 0            | No action                                                                                 |

| 1            | The status flag CLK_STAT[x] is cleared by setting of this bit. (bit always reads as zero) |

Table 16. MPC9894 IDCS Configuration<sup>(1)</sup>

| IDCS_MODE [2:0] | Description | Primary clock | Secondary clock <sup>(2)</sup> | Tertiary clock <sup>(2)</sup> | Quaternary clock <sup>(2)</sup> |

|-----------------|-------------|---------------|--------------------------------|-------------------------------|---------------------------------|

| 000             | Manual      | CLK0          | n/a                            | n/a                           | n/a                             |

| 001             |             | CLK1          | n/a                            | n/a                           | n/a                             |

| 010             |             | CLK2          | n/a                            | n/a                           | n/a                             |

| 011             |             | CLK3          | n/a                            | n/a                           | n/a                             |

| 100             | Automatic   | CLK0          | CLK1                           | CLK2                          | CLK3                            |

| 101             |             | CLK1          | CLK2                           | CLK3                          | CLK0                            |

| 110             |             | CLK2          | CLK3                           | CLK0                          | CLK1                            |

| 111             |             | CLK3          | CLK0                           | CLK1                          | CLK2                            |

<sup>1.</sup> This is a repeat of Table 8.

<sup>2.</sup> For CLK\_VALID[3:0] = 1111 and input clock validity.

# **Device Configuration and Output Enable Register**

The Device Configuration and Output Enable Register is used to individually enable or disable each bank of outputs. Output banks are enabled by setting the corresponding bit to a logic 1 and disabled by setting the bit to a logic 0 as described in Table 21. Output Clock Stop/Enable. The disable logic sets the outputs of the addressed bank synchronously to logic low state (Qx[] = 0 and Qx[] = 1). The clock output enable/stop bits can be set asynchronous to any clock signal without the risk of generating of runt pulses. The

PLL feedback output QFB cannot be disabled when MPC9894 is configured for external feedback.

The Device Configuration Register, bit 6, QUAL\_EN is used to enable or disable all clock input qualifier pins. Asserting this bit enables the Clock Qualifier Input Pins CLK\_VALID[3:0]. Deasserting this bit disables these pins such that inputs on CLK\_VALID[3:0] are ignored.

The INT\_E bit, in bit position 7, is used to enable or disable interrupts from occurring on the INT pin. The setting of the interrupt flag (bit 7 of the Status Register) is unaffected by this bit

Table 17. Device Configuration and Output Clock Enable Register (Register 3 — Read/Write)

| Bit            | 7     | 6       | 5            | 4          | 3         | 2         | 1         | 0         |

|----------------|-------|---------|--------------|------------|-----------|-----------|-----------|-----------|

| Description    | INT_E | QUAL_EN | Slew_Control | Enable_QFB | ENABLE_QA | ENABLE_QB | ENABLE_QC | ENABLE_QD |

| Reset default  | 0     | 0       | 0            | 0          | 0         | 0         | 0         | 0         |

| Preset default | 1     | 1       | 0            | 0          | 1         | 1         | 1         | 1         |

# Table 18. Interrupt Signal (INT) Enable INT\_E

| INT_E | Description                      |  |  |

|-------|----------------------------------|--|--|

| 0     | Interrupt signal INT is disabled |  |  |

| 1     | Interrupt signal INT is enabled  |  |  |

#### Table 19. Input Clock Qualifier Enable QUAL\_EN

| QUAL_EN | Description                                                        |  |  |

|---------|--------------------------------------------------------------------|--|--|

| 0       | CLK_VALID[3:0] are disabled (clock qualifier signals are disabled) |  |  |

| 1       | CLK_VALID[3:0] are enabled (clocks can be qualified)               |  |  |

# Table 20. Slew Control

| Slew_Control | Description                                                     |

|--------------|-----------------------------------------------------------------|

| 0            | Clock slew direction on clock switch is toward the closest edge |

| 1            | Clock slew direction on clock switch is toward the lagging edge |

#### Table 21. Output Clock Stop/Enable

| ENABLE_Qx | Description                                               |  |  |

|-----------|-----------------------------------------------------------|--|--|

| 0         | Output bank x is disabled (clock stop in logic low state) |  |  |

| 1         | Output bank x is enabled                                  |  |  |

# Input and Feedback Divider Configuration Register

Table 22. Input and Feedback Divider Configuration Register (Register 4 — Read/Write)

| Bit            | 7        | 6        | 5        | 4        | 3 | 2        | 1          | 0 |

|----------------|----------|----------|----------|----------|---|----------|------------|---|

| Description    | Reserved | Reserved | Reserved | Reserved |   | Input_FB | 3_Div[3:0] |   |

| Reset default  | n/a      | n/a      | n/a      | n/a      | 0 | 0        | 0          | 0 |

| Preset default | n/a      | n/a      | n/a      | n/a      | 0 | 0        | 1          | 1 |

The Input and Feedback Divider Configuration Register is used to select the input divider value and the feedback divider values. The four bits for Input\_FB\_Div allow 16 combinations of input and feedback divider ratios. Some input and output

frequency ranges may overlap allowing a choice of PLL closed loop bandwidths. This selection may be useful when PLL devices are cascaded.

Table 23. Input\_FB\_Div[3:0]

| Input_FB_Div[3:0] | Input Divider (P) | Feedback Divider (M) |  |  |

|-------------------|-------------------|----------------------|--|--|

| 0000              | 1                 | 16                   |  |  |

| 0001              | 1                 | 12                   |  |  |

| 0010              | 2                 | 12                   |  |  |

| 0011              | 1                 | 8                    |  |  |

| 0100              | 2                 | 16                   |  |  |

| 0101              | res               | served               |  |  |

| 0110              | 2                 | 8                    |  |  |

| 0111              | 3                 | 12                   |  |  |

| 1000              | 4                 | 16                   |  |  |

| 1001              | res               | served               |  |  |

| 1010              | 4                 | 12                   |  |  |

| 1011              | reserved          |                      |  |  |

| 1100              | reserved          |                      |  |  |

| 1101              | reserved          |                      |  |  |

| 1110              | 4                 | 8                    |  |  |

| 1111              | 6                 | 12                   |  |  |

#### **Device Status Register**

The Device Status Register contains a copy of the status SEL\_STAT[1:0], LOCK and CLK\_STAT[3:0] pins. In addition, bit 7 is an INT flag bit, which is used to indicate a setting of a bit in the CLK\_STAT[3:0], a clearing of the LOCK bit and a change in the value of the SEL\_STAT[1:0] bits.

The CLK\_STAT[3:0] bits are sticky and remain set until manually reset through the Mode Configuration Register.

The setting of the register INT bit is reflected on the interrupt pin only if interrupts are enabled. Enabling interrupts is done by the setting of the INT\_E bit which is located in the Device Configuration Register. Reading of the Status Register clears the INT flag.

Table 24. Status Register (Register 5 — Read Only)

| Bit         | 7                                  | 6                                               | 5             | 4 | 3   | 2                                 | 1                              | 0 |

|-------------|------------------------------------|-------------------------------------------------|---------------|---|-----|-----------------------------------|--------------------------------|---|

| Description | Inverse of $\overline{\text{INT}}$ | CLK_STAT[3:0<br>Status of CLK3<br>Copy of CLK_5 | 3, CLK2, CLK1 | ` | xy) | LOCK<br>Inverse of LOCK<br>signal | SEL_STAT[1:0]<br>Copy of SEL_S | • |

# **Output Power-Up Register**

The Output Power-Up Register configures each of the 8 LVPECL outputs for either power-up or a power-down state. The use of these bits allows power consumption to be

reduced when all of the clock outputs are not used. Placing an output in the power-down condition is not synchronous with the clock edges.

Table 25. Output Power-Up Register (Register 6 — Read/Write)

| Bit            | 7       | 6       | 5       | 4       | 3       | 2        | 1       | 0       |

|----------------|---------|---------|---------|---------|---------|----------|---------|---------|

| Description    | PWR_QD1 | PWR_QD0 | PWR_QC1 | PWR_QC0 | PWR_QB1 | PWR_QB01 | PWR_QA1 | PWR_QA0 |

| Reset Default  | 0       | 0       | 0       | 0       | 0       | 0        | 0       | 0       |

| Preset Default | 1       | 1       | 1       | 1       | 1       | 1        | 1       | 1       |

# **Table 26. Clock Output Power-Up Bits**

| PWR_Qxx | Description       |

|---------|-------------------|

| 0       | Output Power-Down |

| 1       | Output Power-Up   |

#### Feedback Power-Up Register

The Feedback Power-Up register bit 0 is used to configure the MPC9894 feedback output in either a power-up state or a power-down state. Note this register bit is valid for internal

feedback configuration only. When external feedback is selected QFB is always enabled and in a power-up state. The remaining bits of this register are unused and read as a logic 0.

Table 27. Feedback Power-Up Register (Register 7 — Read/Write)

| Bit            | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0       |

|----------------|---|---|---|---|---|---|---|---------|

| Description    |   |   |   |   |   |   |   | PWR_QFB |

| Reset Default  |   |   |   |   |   |   |   | 0       |

| Preset Default |   |   |   |   |   |   |   | 1       |

# Table 28. Feedback Output Power-Up Bit

| PWR_QFB | Description                |

|---------|----------------------------|

| 0       | Feedback Output Power-Down |

| 1       | Feedback Output Power-Up   |

# IEEE STD.1149.1(JTAG)

This section describes the IEEE Std. 1149.1 compliant Test Access Port (TAP) and Boundary Scan Architecture implementation in the MPC9894. Special private instructions are provided to assist in production test control. These instructions combined with control of the test mode inputs

and the use of shared inputs and outputs provide for full production test mode access and control.

#### **Test Access Port Interface Signals**

Table 29 lists the TAP interface signals and their descriptions.

**Table 29. TAP Interface Signals**

| Signal Name | Description      | Function                             | Direction | Active State |

|-------------|------------------|--------------------------------------|-----------|--------------|

| TCK         | Test Clock       | Test logic clock.                    | Input     | _            |

| TMS         | Test Mode Select | TAP mode control input.              | Input     | _            |

| TDI         | Test Data In     | Serial test instruction/data input.  | Input     | _            |

| TRST_B      | Test Reset Bar   | Asynchronous test controller reset.  | Input     | _            |

| TDO         | Test Data Out    | Serial test instruction/data output. | Output    | _            |

#### **Instruction Register**

#### **Table 30. Instruction Register**

| Bit Position     | 4  | 3 | 2 | 1 | 0 |  |  |  |  |

|------------------|----|---|---|---|---|--|--|--|--|

| Field            | IR |   |   |   |   |  |  |  |  |

| Capture-IR Value | 0  | 0 | 0 | 0 | 1 |  |  |  |  |

#### Instructions

Table 31 lists the public instructions provided in the implementation and their instruction codes. Public

instructions are accessible by the customer for board test and may also be used for production chip test.

**Table 31. TAP Controller Public Instructions**

| Instruction | Code  | Enabled Serial Test Data Path |

|-------------|-------|-------------------------------|

| BYPASS      | 11111 | Bypass Register               |

| CLAMP       | 01100 | Bypass Register               |

| EXTEST      | 00000 | Boundary Scan Register        |

| HIGHZ       | 01001 | Bypass Register               |

| IDCODE      | 00001 | ID Register                   |

| SAMPLE      | 00010 | Boundary Scan Register        |

#### **Boundary-Scan Register**

A full description of the boundary scan register may be found in the BSDL file.

# Device Identification Register (0x0281D01D)

**Table 32. Device Identification Register**

| Bit<br>Position | 31 | 30  | 29   | 28 | 27 | 26          | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13   | 12    | 11   | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|-----------------|----|-----|------|----|----|-------------|----|----|----|----|----|----|----|----|----|----|----|----|------|-------|------|----|---|---|---|---|---|---|---|---|---|---|

| Field           |    | Ver | sion |    |    | Part Number |    |    |    |    |    |    |    |    |    |    |    | M  | anuf | factu | ırer | ID |   |   |   |   |   |   |   |   |   |   |

| Value           | 0  | 0   | 0    | 0  | 0  | 0           | 1  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 1  | 1  | 0    | 1     | 0    | 0  | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | 1 |

#### POWER SUPPLY CONFIGURATION

The MPC9894 operates from either a 3.3 V or 2.5 V voltage supply for the device core. The pin SEL\_2P5V is used to logically indicate the core supply voltage. This selection is done by setting the pin to a logic 1 for 2.5 V or logic 0 for 3.3 V operation.

The input and output supply voltage may be set for either 3.3 V or 2.5 V and can be individually set for inputs and banks

of outputs. Table 33. Power Supply Configuration lists the supply pins and what pin or group of pins are associated with each supply. Note, that for output skew and SPO specifications to be valid the input, feedback input and output, and the output bank must all be at the same voltage level.

**Table 33. Power Supply Configuration**

| Supply Voltage                   | Description                                                                                                     | Value                        |

|----------------------------------|-----------------------------------------------------------------------------------------------------------------|------------------------------|

| $V_{DD}$                         | Positive power supply for the device core, output status and control inputs. (3.3 V or 2.5 V)                   | 3.3 V or 2.5 V               |

| $V_{DDAB}$                       | Supply voltage for output banks A and B (QA0 through QB1)                                                       | 3.3 V or 2.5 V               |

| $V_{DDCD}$                       | Supply voltage for output banks A and B (QC0 through QD1) and QFB                                               | 3.3 V or 2.5 V               |

| V <sub>DDIC</sub> <sup>(1)</sup> | Supply voltage for differential inputs clock inputs CLK0 to CLK3 and FB_IN                                      | 3.3 V or 2.5 V               |

| $V_{DDA}$                        | Clean supply for Analog portions of the PLL (This voltage is derived via an RC filter from the $V_{DD}$ supply) | Derived from V <sub>DD</sub> |

<sup>1.</sup> V<sub>DDIC</sub> (Supply of FB\_IN) must be equal to V<sub>DDCD</sub> (Supply of QFB) to ensure the SPO specification is met.

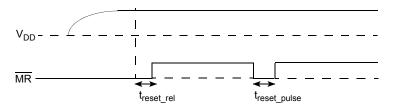

# Power Supply Sequencing and MR Operation

Figure 5 defines the release time and the minimum pulse length for  $\overline{\text{MR}}$  pin. The  $\overline{\text{MR}}$  release time is based upon the power supply being stable and within  $V_{DD}$  specifications. Refer to Table 39 for actual parameter values. The MPC9894

may be configured after release of reset and the outputs will be stable for use after lock indication is obtained.

$V_{DD}$  must ramp up prior to or concurrent with the other power supply pins. It is recommended that the maximum slew rate for the  $V_{DD}$  supply not exceed 0.5 V/ms.

Figure 5. MR Operation

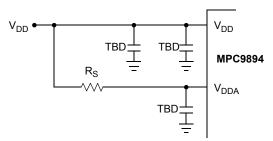

Figure 6. V<sub>CC</sub> Power Supply Bypass

#### **Power Supply Bypassing**