# MITSUBISHI MICROCOMPUTERS

# **7451 Group**

# SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

#### DESCRIPTION

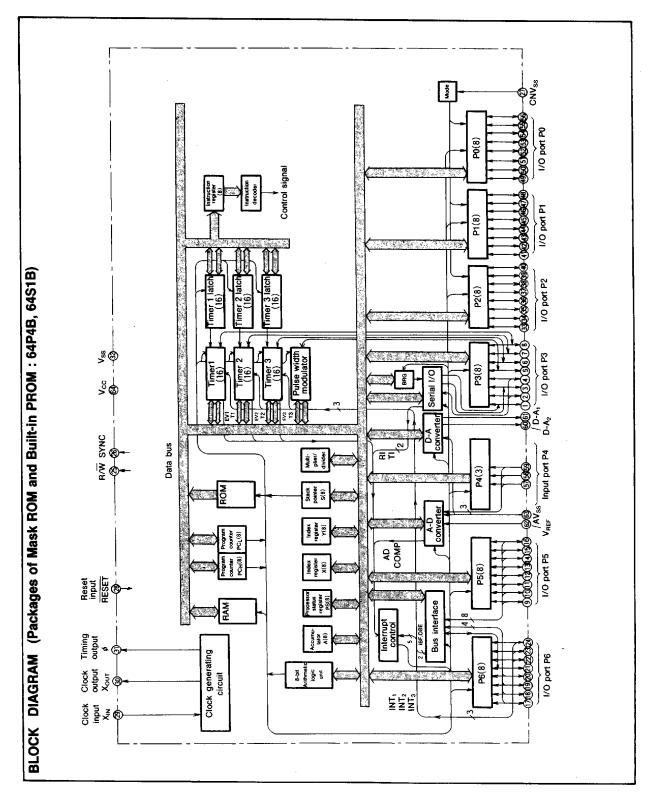

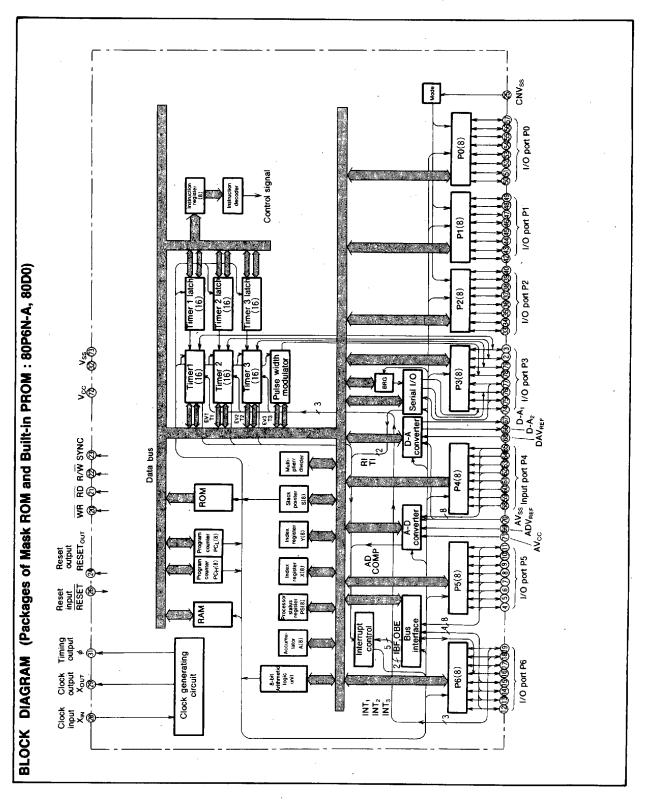

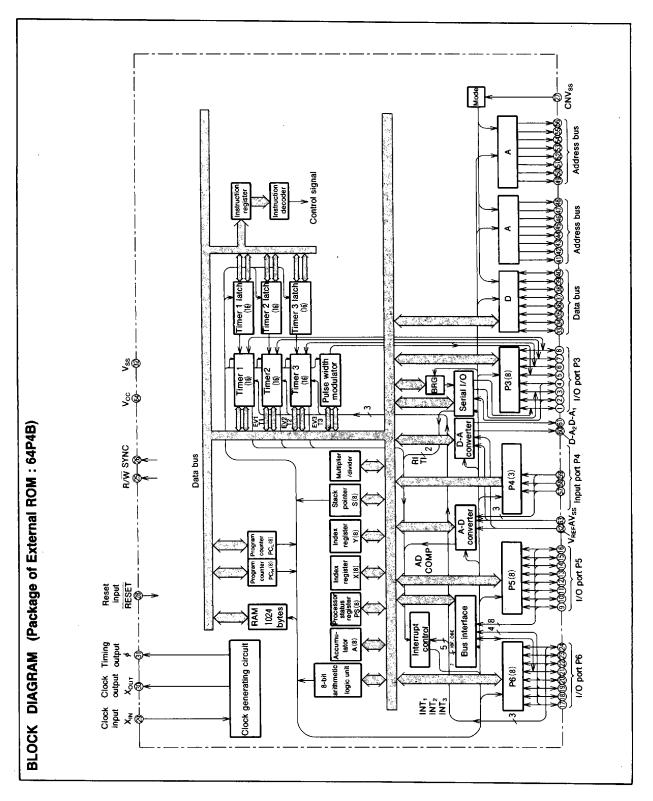

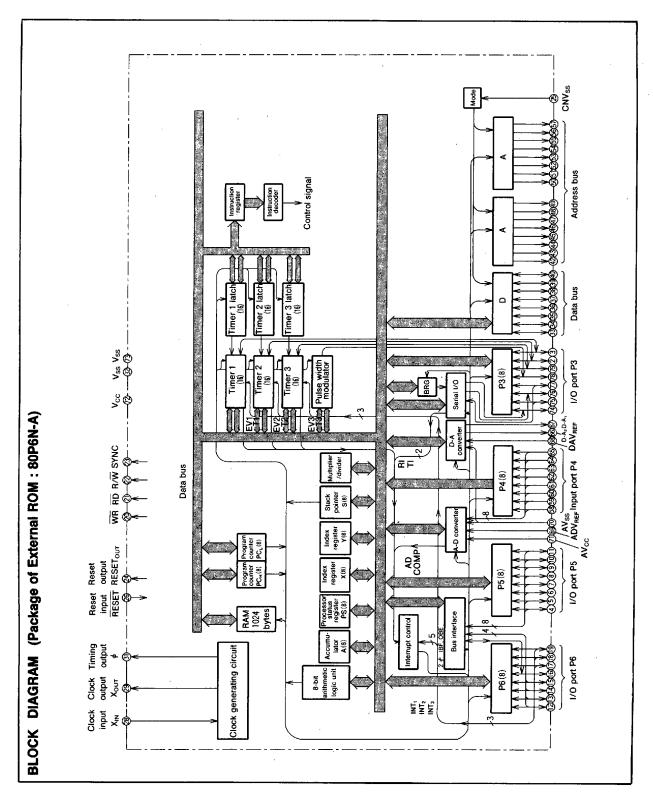

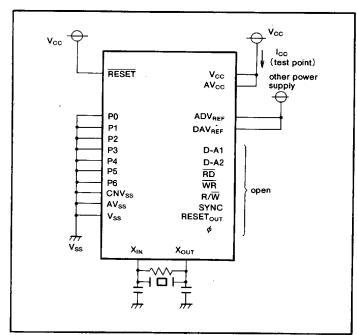

The 7451 group is a single-chip microcomputer designed with CMOS technology.

In addition to its simple instruction sets, the ROM, RAM, and I/O addresses are placed on the same memory map to enable easy programming.

It is suited for office automation equipment and control devices. The low power consumption made by the use of a CMOS process makes it especially suitable for battery powered devices requiring low power consumption. It also has a unique feature that enables it to be used as a slave microcomputer.

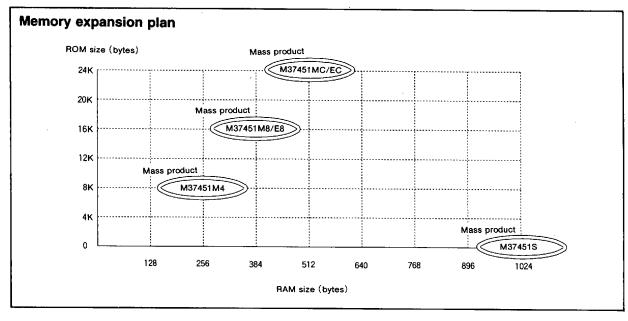

For details on availability of microcomputers in the 7451 group, refer to the section on group expansion.

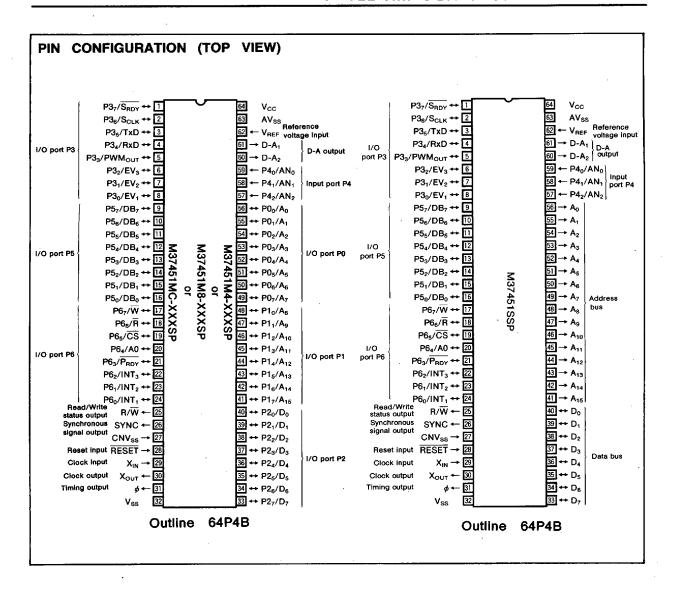

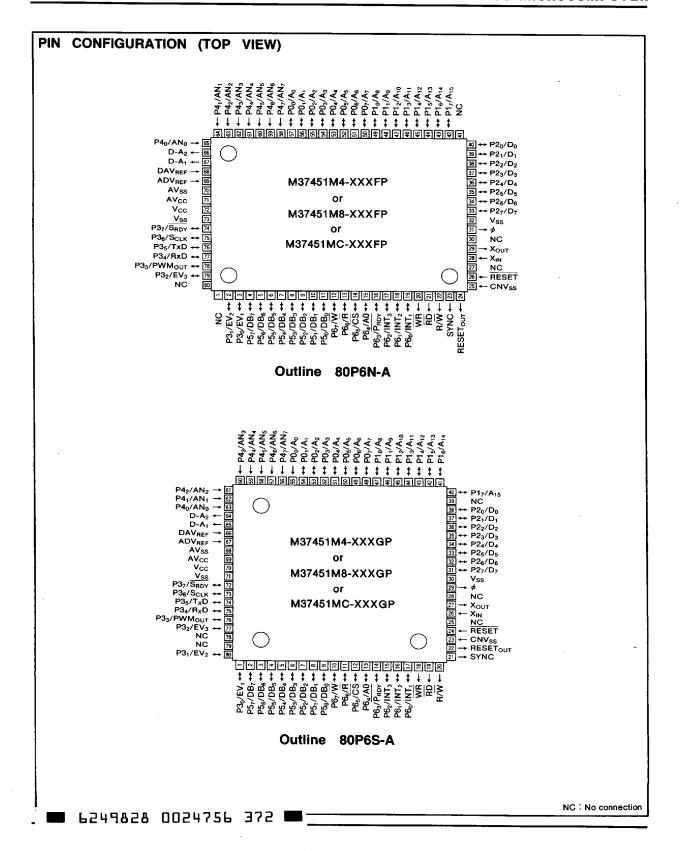

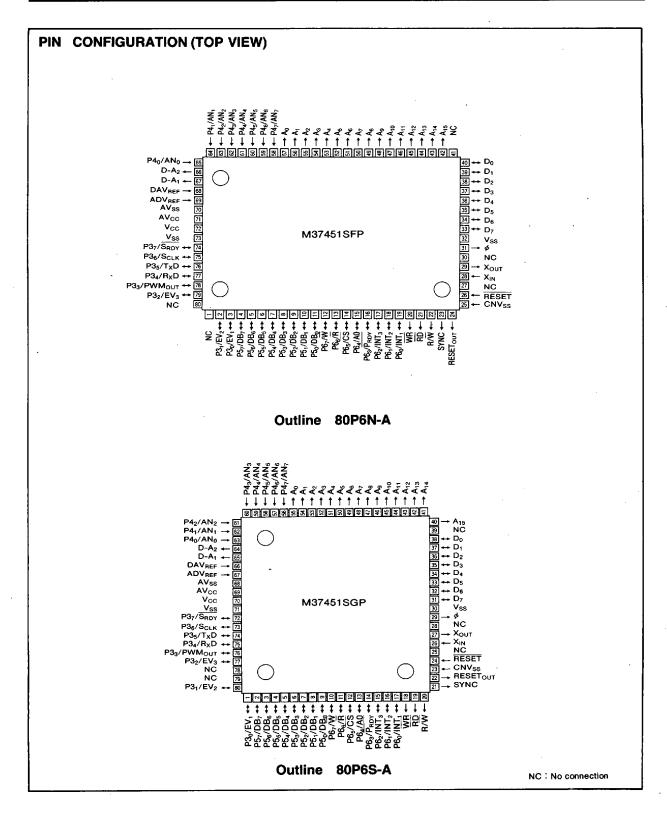

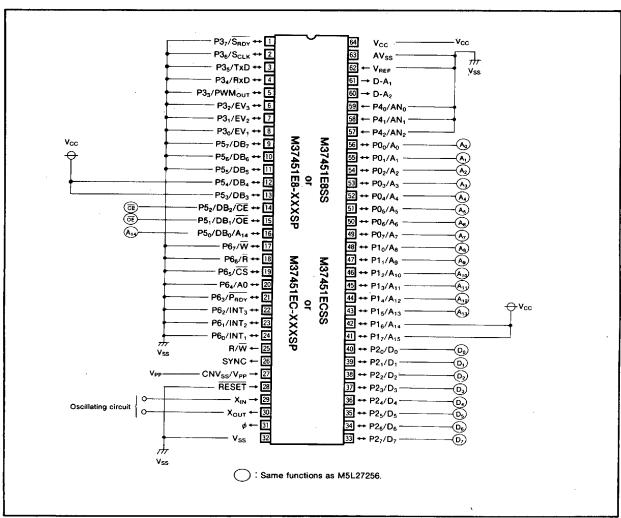

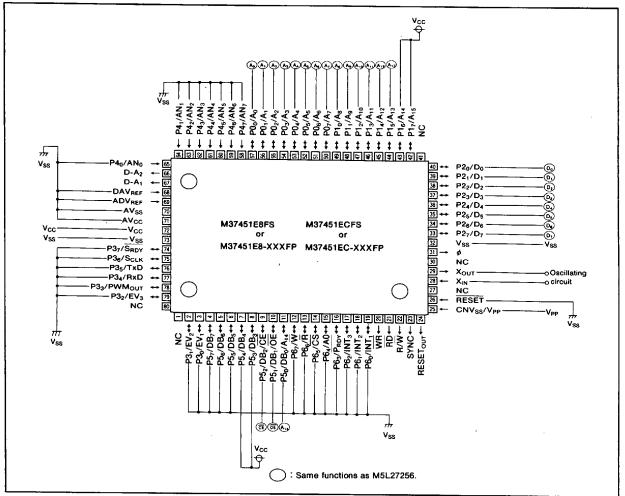

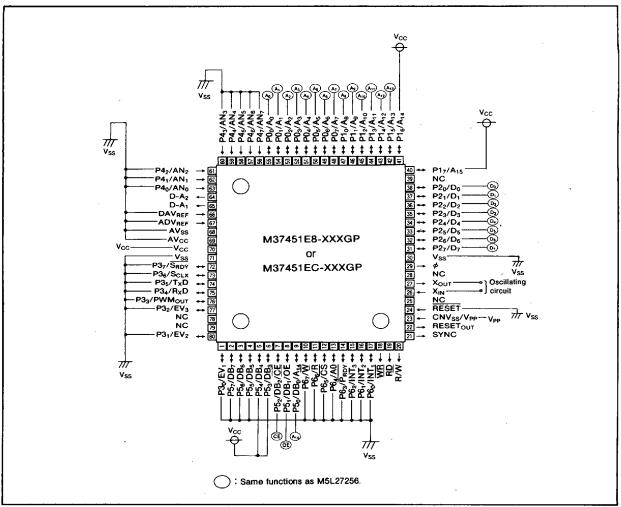

The number of analog input pins for the 80-pin model (FP, GP version) is different from the 64-pin model (SP version). In addition, the 80-pin model has special pins for  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , RESET<sub>OUT</sub>, DAV<sub>REF</sub>, ADV<sub>REF</sub>, AV<sub>CC</sub> and the 64-pin model has a special V<sub>REF</sub> pin.

#### **FEATURES**

| • | Basic machine-language instructions 71                               |

|---|----------------------------------------------------------------------|

| • | The minimum instruction execution time                               |

|   | (at 12.5MHz oscillation frequency) ······ 0.64µs                     |

| • | Memory size                                                          |

|   | ROM ······ 0K to 24K bytes                                           |

|   | RAM256 to 1024 bytes                                                 |

| • | Power source voltage ······5V±10%                                    |

| • | Power dissipation                                                    |

|   | (at 12.5MHz oscillation frequency) ·······40mW                       |

| • | Subroutine nesting ······· 96 levels max.(M37451M4/E4)               |

|   | 96 levels max.(M37451M8/E8)                                          |

|   | 128 levels max.(M37451MC/EC/S)                                       |

| • | Interrupt                                                            |

| • | Master CPU bus interface ·······1 byte                               |

| • | 16-bit timers ······3                                                |

| • | 8-bit timer (Serial I/O use) ······1                                 |

| • | Serial I/O (UART or clock synchronous) ······1                       |

| • | A-D converter (8-bit resolution) 3 channels (DIP)                    |

| _ | 8 channels (QFP)                                                     |

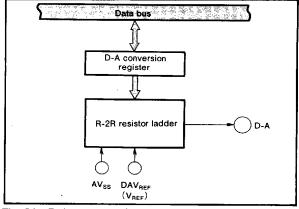

| • | D-A converter (8-bit resolution) ····· 2 channels                    |

| • | PWM output with 8-bit prescaler                                      |

|   | (Either resolution 8 bit or 16 bit is software selectable) ···· 1    |

| • | Programmable I/O ports                                               |

|   | (mask ROM version and PROM version)                                  |

| _ | (External ROM version)                                               |

| _ | Input port (Port P4)3(DIP), 8(QFP)                                   |

| • | Output ports (Ports D-A <sub>1</sub> , D-A <sub>2</sub> ) $\cdots 2$ |

#### **APPLICATION**

Slave controller for PPCs, facsimiles, and page printers. HDD, optical disk, inverter, and industrial motor controllers. Industrial robots and machines.

■ 6249828 0024754 5TT

**6249828 0024755 436**

**6249828 0024757 209**

**--** 6249828 0024758 145 **--**

**■** 6249828 0024759 081 ■

■ 157 £37428 0024761 73T

# PIN DESCRIPTION (mask ROM version and PROM version)

| Pin                                                                     | Name                        | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                              |  |  |  |

|-------------------------------------------------------------------------|-----------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>CC</sub> ,<br>V <sub>SS</sub>                                    | Power source                |                  | Apply voltage of 5V±10% to V <sub>CC</sub> , and 0V to V <sub>SS</sub> .                                                                                                                                                                                                                               |  |  |  |

| CNVss                                                                   | CNV <sub>SS</sub>           | Input            | Controls the processor mode of the chip. Normally connected to V <sub>SS</sub> or V <sub>CC</sub> .                                                                                                                                                                                                    |  |  |  |

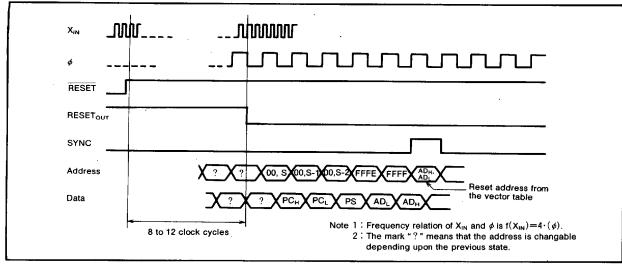

| RESET                                                                   | Reset input                 | Input            | To enter the reset state, the reset input pin must be kept at a "L" for 8 or more clock cycles (under normal V <sub>CC</sub> conditions). If more time is needed for the crystal oscillator to stabilize, this "L" condition should be maintained for the required time.                               |  |  |  |

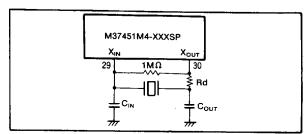

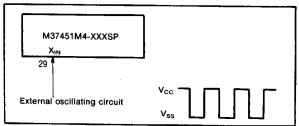

| XIN                                                                     | Clock input                 | Input            | This chip has an internal clock generating circuit. To control generating frequency, an external ceramic or                                                                                                                                                                                            |  |  |  |

| Хоит                                                                    | Clock output                | Output           | quartz crystal oscillator is connected between the $X_{IN}$ and $X_{OUT}$ pins. If an external clock is used, the cloc source should be connected to the $X_{IN}$ pin and the $X_{OUT}$ pin should be left open.                                                                                       |  |  |  |

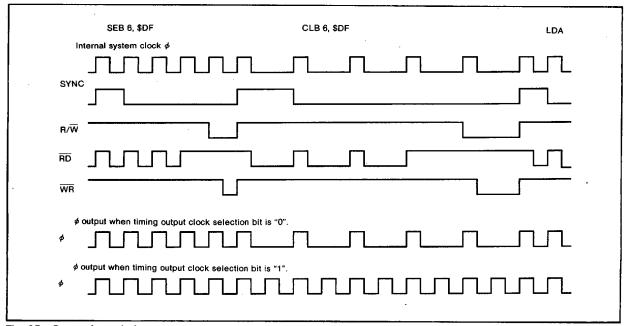

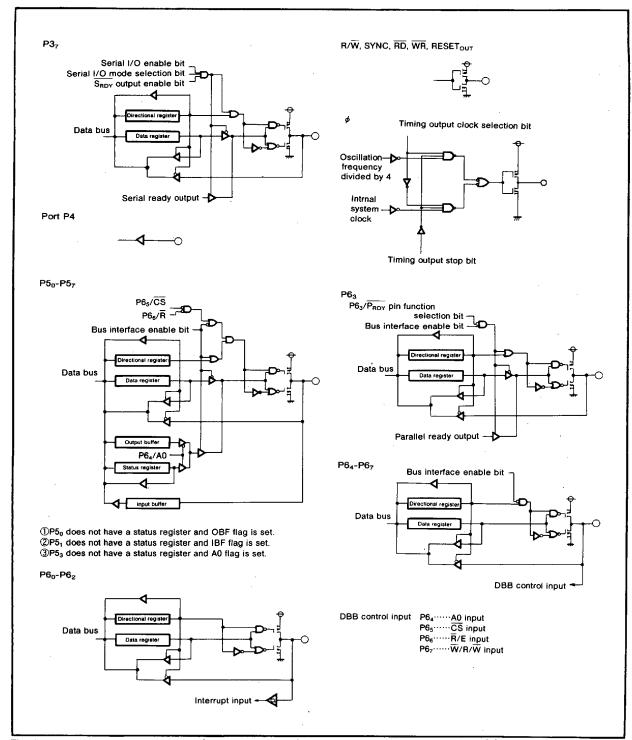

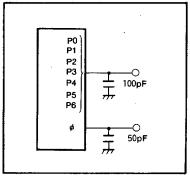

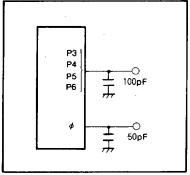

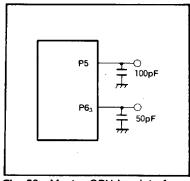

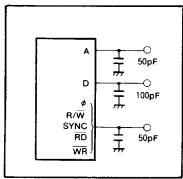

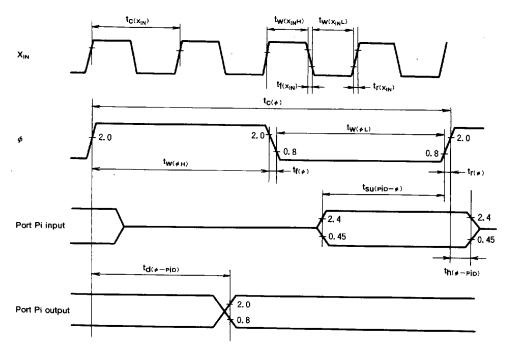

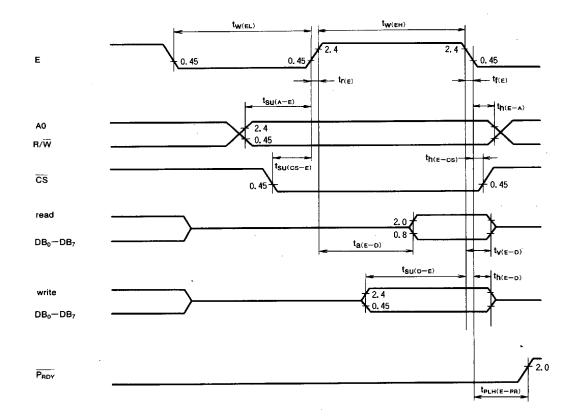

| ø                                                                       | Timing output               | Output           | Normally outputs clock consisting of oscillating frequency divided by four.                                                                                                                                                                                                                            |  |  |  |

| SYNC                                                                    | Synchronous signal output   | Output           | This signal is output "H" during operation code fetch and is used to control single stepping of programs.                                                                                                                                                                                              |  |  |  |

| R/W                                                                     | Read/Write<br>status output | Output           | This signal determines the direction of the data bus. It is "H" during read and "L" during write.                                                                                                                                                                                                      |  |  |  |

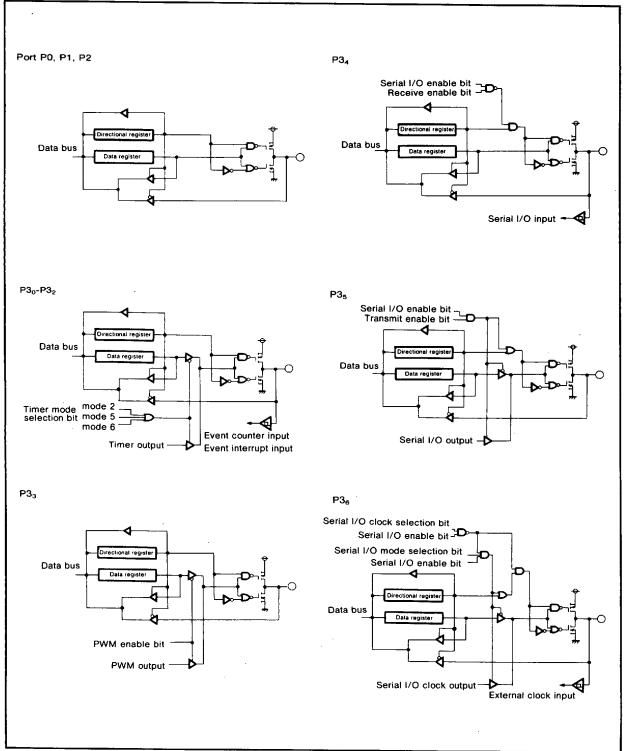

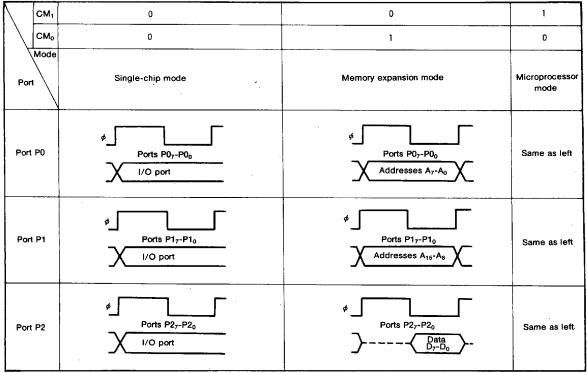

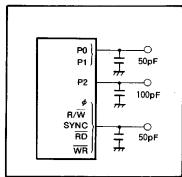

| P0 <sub>0</sub> -P0 <sub>7</sub>                                        | I/O port P0                 | 1/0              | Port P0 is an 8-bit I/O port with directional registers allowing each I/O bit to be individually programmed a input or output. The output structure is CMOS output. The low-order bits of the address are output except in single-chip mode.                                                           |  |  |  |

| P1 <sub>0</sub> -P1 <sub>7</sub>                                        | I/O port P1                 | 1/0              | Port P1 is an 8-bit I/O port and has basically the same functions as port P0. The high-order bits of the address are output except in single-chip mode.                                                                                                                                                |  |  |  |

| P2 <sub>0</sub> -P2 <sub>7</sub>                                        | I/O port P2                 | 1/0              | Port P2 is an 8-bit I/O port and has basically the same functions as port P0. Used as data bus except single-chip mode.                                                                                                                                                                                |  |  |  |

| P3 <sub>0</sub> -P3 <sub>7</sub>                                        | I/O port P3                 | 1/0              | Port P3 is an 8-bit I/O port and has basically the same functions as port P0. Serial I/O, PWM output, of event I/O function can be selected with a program.                                                                                                                                            |  |  |  |

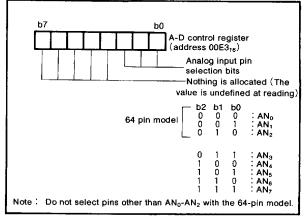

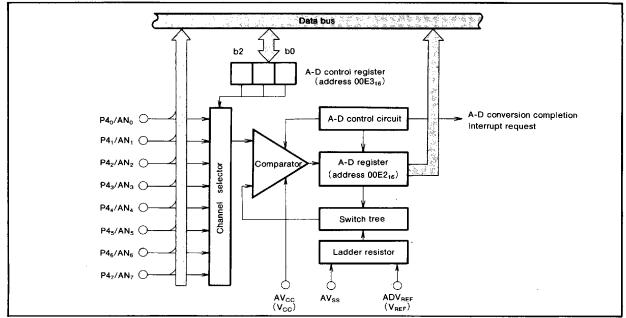

| P4 <sub>0</sub> -P4 <sub>2</sub><br>(P4 <sub>0</sub> -P4 <sub>7</sub> ) | Input port P4               | Input            | Analog input pin for the A-D converter. The 64-pin model has three pins and the 80-pin model has eighns. They may also be used as digital input pins.                                                                                                                                                  |  |  |  |

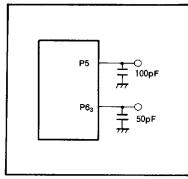

| P5 <sub>0</sub> -P5 <sub>7</sub>                                        | I/O port P5                 | 1/0              | Port P5 is an 8-bit I/O port and has basically the same functions as port P0. This port functions as an 8-data bus for the master CPU when slave mode is selected with a program.                                                                                                                      |  |  |  |

| P6 <sub>0</sub> -P6 <sub>7</sub>                                        | I/O port P6                 | 1/0              | Port P6 is an 8-bit I/O port and has basically the same function as port P0. Pins P6 <sub>3</sub> -P6 <sub>7</sub> change to a contr<br>bus for the master CPU when slave mode is selected with a program. Pins P6 <sub>0</sub> -P6 <sub>2</sub> may be programme<br>as external interrupt input pins. |  |  |  |

| D-A <sub>1</sub> , D-A <sub>2</sub>                                     | D-A output                  | Output           | Analog signal from D-A converter is output.                                                                                                                                                                                                                                                            |  |  |  |

| V <sub>REF</sub>                                                        | Reference voltage input     | Input            | Reference voltage input pin for A-D and D-A converter. This pin is for 64-pin model only.                                                                                                                                                                                                              |  |  |  |

| ADV <sub>REF</sub>                                                      | A-D reference voltage input | Input            | Reference voltage input pin for A-D converter. This pin is for 80-pin model only.                                                                                                                                                                                                                      |  |  |  |

| DAVREF                                                                  | D-A reference voltage input | Input            | Reference voltage input pin for D-A converter. This pin is for 80-pin model only.                                                                                                                                                                                                                      |  |  |  |

| AV <sub>SS</sub>                                                        | Analog power supply         |                  | Ground level input pln for A-D and D-A converter. Same voltage as V <sub>SS</sub> is applied.                                                                                                                                                                                                          |  |  |  |

| AVoc                                                                    | Analog power supply         |                  | Power supply input pin for A-D converter. This pin is for 80-pin model only. Same voltage as $V_{CC}$ is applied in the case of the 64-pin model, $AV_{CC}$ is connected to $V_{CC}$ internally.                                                                                                       |  |  |  |

| RD                                                                      | Read signal output          | Output           | Control signal output as active "L" when valid data is read from data bus. This pin is for 80-pin model only                                                                                                                                                                                           |  |  |  |

| WR                                                                      | Write signal output         | Output           | Control signal output as active "L" when writing data from data bus to external component. This pin is 80-pin model only.                                                                                                                                                                              |  |  |  |

| RESETOUT                                                                | Reset output                | Output           | Control signal output as active "H" during reset. It is used as a reset output signal for peripheral comp nents. This pin is for 80-pin model only.                                                                                                                                                    |  |  |  |

**■** 6249828 0024762 676 **■**

## PIN DESCRIPTION (EPROM mode of PROM version)

| Pin                                                                     | Name                           | Input/<br>Output | Functions                                                                                                                                                                                                                                                          |  |  |

|-------------------------------------------------------------------------|--------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| V <sub>CC</sub> , V <sub>SS</sub>                                       | Power source                   | -                | Apply voltage of 5V±10% to V <sub>CC</sub> , and 0V to V <sub>SS</sub> .                                                                                                                                                                                           |  |  |

| CNV <sub>SS</sub> /V <sub>PP</sub>                                      | V <sub>PP</sub>                | Input            | Connect to V <sub>PP</sub> when programming or verifing.                                                                                                                                                                                                           |  |  |

| RESET                                                                   | Reset input                    | Input            | Connect to V <sub>SS</sub>                                                                                                                                                                                                                                         |  |  |

| XIN                                                                     | Clock input                    | Input            | Connect a ceramic or a quartz crystal oscillator between X <sub>IN</sub> and X <sub>OUT</sub> for clock oscillation.                                                                                                                                               |  |  |

| Хоит                                                                    | Clock output                   | Output           |                                                                                                                                                                                                                                                                    |  |  |

| φ                                                                       | Timing output                  | Output           | For timing output                                                                                                                                                                                                                                                  |  |  |

| SYNC                                                                    | Synchronous signal output      | Output           | Kept to open ("L" signal is output).                                                                                                                                                                                                                               |  |  |

| R/W                                                                     | Read/Write<br>status output    | Output           | Kept to open ("H" signal is output).                                                                                                                                                                                                                               |  |  |

| P0 <sub>0</sub> P0 <sub>7</sub>                                         | I/O port P0                    | Input            | P0 works as the lower 8-bit address input.                                                                                                                                                                                                                         |  |  |

| P1 <sub>0</sub> —P1 <sub>7</sub>                                        | I/O port P1                    | Input            | P1 <sub>0</sub> -P1 <sub>5</sub> work as the higher 6-bit address input. P1 <sub>6</sub> and P1 <sub>7</sub> connect to V <sub>CC</sub> .                                                                                                                          |  |  |

| P2 <sub>0</sub> -P2 <sub>7</sub>                                        | I/O port P2                    | 1/0              | P2 works as an 8-bit data bus.                                                                                                                                                                                                                                     |  |  |

| P3 <sub>0</sub> —P3 <sub>7</sub>                                        | I/O port P3                    | Input            | Connect to V <sub>SS</sub>                                                                                                                                                                                                                                         |  |  |

| P4 <sub>0</sub> -P4 <sub>7</sub><br>(P4 <sub>0</sub> -P4 <sub>2</sub> ) | Input port P4                  | Input            | Connect to V <sub>SS</sub> . The 64-pin model has only three pins P4 <sub>0</sub> —P4 <sub>2</sub> .                                                                                                                                                               |  |  |

| P5 <sub>0</sub> P5 <sub>7</sub>                                         | I/O port P5                    | Input            | P5 <sub>0</sub> , P5 <sub>1</sub> , P5 <sub>2</sub> works as A <sub>14</sub> , $\overline{OE}$ , and $\overline{CE}$ inputs respectively. Connect P5 <sub>3</sub> and P5 <sub>4</sub> to V <sub>CC</sub> and P5 <sub>5</sub> -P5 <sub>7</sub> to V <sub>SS</sub> . |  |  |

| P6 <sub>0</sub> -P6 <sub>7</sub>                                        | I/O port P6                    | Input            | Connect to V <sub>SS</sub> .                                                                                                                                                                                                                                       |  |  |

| D-A <sub>1</sub> , D-A <sub>2</sub>                                     | D-A output                     | Output           | Kept to open.                                                                                                                                                                                                                                                      |  |  |

| V <sub>REF</sub>                                                        | Reference voltage input        | Input            | Connect to V <sub>SS</sub> . This pin is for 64-pin model only.                                                                                                                                                                                                    |  |  |

| ADV <sub>REF</sub>                                                      | A-D reference<br>voltage input | Input            | Connect to V <sub>SS</sub> . This pin is for 80-pin model only.                                                                                                                                                                                                    |  |  |

| DAV <sub>REF</sub>                                                      | D-A reference voltage input    | Input            | Connect to V <sub>SS</sub> . This pin is for 80-pin model only.                                                                                                                                                                                                    |  |  |

| AV <sub>ss</sub>                                                        | Analog power                   | Input            | Connect to V <sub>SS</sub> .                                                                                                                                                                                                                                       |  |  |

| AV <sub>CC</sub>                                                        | Analog power                   | Input            | Connect to V <sub>CC</sub> or V <sub>SS</sub> . This pin is for 80-pin model only.                                                                                                                                                                                 |  |  |

| RD                                                                      | Read signal output             | Output           | Kept to open ("H" signal is output). This pin is for 80-pin model only.                                                                                                                                                                                            |  |  |

| WR                                                                      | Write signal output            | Output           | Kept to open ("H" signal is output). This pin is for 80-pin model only.                                                                                                                                                                                            |  |  |

| RESETOUT                                                                | Reset output                   | Output           | Kept to open ("H" signal is output). This pin is for 80-pin model only.                                                                                                                                                                                            |  |  |

**■** 6249828 0024763 502 **■**

## PIN DESCRIPTION (External ROM version)

| Pin                                                                     | Name                        | Input/<br>Output | Functions                                                                                                                                                                                                                                                                       |  |  |  |

|-------------------------------------------------------------------------|-----------------------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V <sub>cc</sub> ,<br>V <sub>ss</sub>                                    | Power source                |                  | Apply voltage of 5V±10% to V <sub>CC</sub> , and 0V to V <sub>SS</sub> .                                                                                                                                                                                                        |  |  |  |

| CNV <sub>ss</sub>                                                       | CNV <sub>SS</sub>           | Input            | This is connected to V <sub>CC</sub> .                                                                                                                                                                                                                                          |  |  |  |

| RESET                                                                   | Reset input                 | Input            | To enter the reset state, the reset input pin must be kept at a "L" for 8 or more clock cycles(under norm $V_{CC}$ conditions). If more time is needed for the crystal oscillator to stabilize, this "L" condition should maintained for the required time.                     |  |  |  |

| XIN                                                                     | Clock input                 | Input            | This chip has an internal clock generating circuit. To control generating frequency, an external ceramic or a                                                                                                                                                                   |  |  |  |

| X <sub>OUT</sub>                                                        | Clock output                | Output           | quartz-crystal oscillator is connected between the $X_{\text{IN}}$ and $X_{\text{OUT}}$ pins. If an external clock is used, the clock source should be connected to the $X_{\text{IN}}$ pin and the $X_{\text{OUT}}$ pin should be left open.                                   |  |  |  |

| φ                                                                       | Timing output               | Output           | Normally outputs clock consisting of oscillating frequency divided by four.                                                                                                                                                                                                     |  |  |  |

| SYNC                                                                    | Synchronous signal output   | Output           | This signal is output "H" during operation code fetch and is used to control single stepping of programs.                                                                                                                                                                       |  |  |  |

| R/W                                                                     | Read/Write<br>status output | Output           | This signal determines the direction of the data bus. It is "H" during read and "L" during write                                                                                                                                                                                |  |  |  |

| A <sub>0</sub> -A <sub>15</sub>                                         | Address bus                 | Output           | This is 16-bit address bus.                                                                                                                                                                                                                                                     |  |  |  |

| D <sub>0</sub> -D <sub>7</sub>                                          | Data bus                    | 1/0              | This is 8-bit data bus.                                                                                                                                                                                                                                                         |  |  |  |

| P3 <sub>0</sub> -P3 <sub>7</sub>                                        | Input/Output port P3        | 1/0              | Port P3 is an 8-bit I/O port with directional registers allowing each I/O bit to be individually programed as input or output. The output structure is CMOS output. Serial I/O, PWM output, or even I/O function can be selected with a program.                                |  |  |  |

| P4 <sub>0</sub> -P4 <sub>2</sub><br>(P4 <sub>0</sub> -P4 <sub>7</sub> ) | Input port P4               | Input            | Analog input pin for the A-D converter. The 64-pin model has three pins and the 80-pin model has eight pins. They may also be used as digital input pins.                                                                                                                       |  |  |  |

| P5 <sub>0</sub> -P5 <sub>7</sub>                                        | Input/Output port P5        | 1/0              | An 8-bit input/output port with the same function as P3. This port functions as an 8-bit data bus for the master CPU when slave mode is selected with a program.                                                                                                                |  |  |  |

| P6 <sub>0</sub> -P6 <sub>7</sub>                                        | Input/Output port P6        | 1/0              | An 8-bit input/output port with the same function as P3. Pins P6 <sub>3</sub> -P6 <sub>7</sub> change to a control bus for the master CPU when slave mode is selected with a program. Pins P6 <sub>0</sub> -P6 <sub>2</sub> may be programmed as external interrupt input pins. |  |  |  |

| D-A <sub>1</sub> , D-A <sub>2</sub>                                     | D-A output                  | Output           | Analog signal from D-A converter is output.                                                                                                                                                                                                                                     |  |  |  |

| V <sub>REF</sub>                                                        | Reference voltage input     | Input            | Reference voltage input pin for A-D and D-A converter. This pin is for 64-pin model only.                                                                                                                                                                                       |  |  |  |

| ADV <sub>REF</sub>                                                      | A-D reference voltage input | Input            | Reference voltage input pin for A-D converter. This pin is for 80-pin model only.                                                                                                                                                                                               |  |  |  |

| DAV <sub>REF</sub>                                                      | D-A reference voltage input | Input            | Reference voltage input pin for D-A converter. This pin is for 80-pin model only.                                                                                                                                                                                               |  |  |  |

| AV <sub>SS</sub>                                                        | Analog power supply         |                  | Ground level input pin for A-D and D-A converter. Same voltage as V <sub>SS</sub> is applied.                                                                                                                                                                                   |  |  |  |

| AVcc                                                                    | Analog power supply         |                  | Power supply input pin for A-D converter. This pin is for 80-pin model only. Same voltage as V <sub>CC</sub> is applied. In the case of the 64-pin model AV <sub>CC</sub> is connected to V <sub>CC</sub> internally.                                                           |  |  |  |

| RD                                                                      | Read signal output          | Output           | Control signal output as active "L" when valid data is read from data bus. This pin is for 80-pin model only.                                                                                                                                                                   |  |  |  |

| WR                                                                      | Write signal output         | Output           | Control signal output as active "L" when writing data from data bus to external component. This pin is for 80-pin model only.                                                                                                                                                   |  |  |  |

| RESETOUT                                                                | Reset output                | Output           | Control signal output as active "H" during reset. It is used as a reset output signal for peripheral components. This pin is for 80-pin model only.                                                                                                                             |  |  |  |

**■** 6249828 0024764 449 **■**

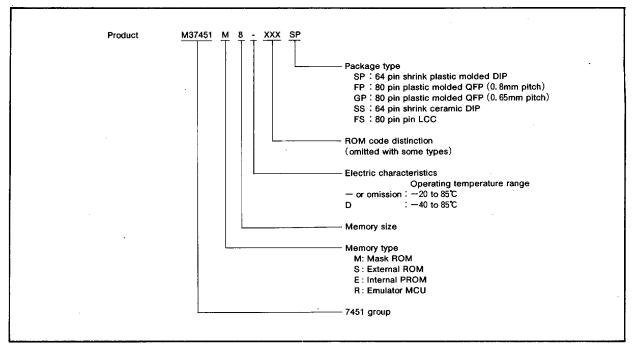

## PART NUMBERING

## **GROUP EXPANSION**

**--** 6249828 0024766 233 **--**

## Currently supported products listed below

As of May 1996

| Product        | (P) ROM size (byte) | RAM size (byte) | Package | Remarks                                |

|----------------|---------------------|-----------------|---------|----------------------------------------|

| M37451M4-XXXSP |                     | ·               | 64P4B   | Mask ROM version                       |

| M37451M4DXXXSP |                     |                 | 64P4B   | Extended operating temperature version |

| M37451M4-XXXFP | 014                 | 050             | DODON A | Mask ROM version                       |

| M37451M4DXXXFP | 8K                  | 256             | 80P6N-A | Extended operating temperature version |

| M37451M4-XXXGP |                     |                 | 80P6S-A | Mask ROM version                       |

| M37451M8-XXXSP |                     |                 |         | Mask ROM version                       |

| M37451M8DXXXSP |                     |                 |         | Extended operating temperature version |

| M37451E8-XXXSP |                     |                 | 64P4B   | One Time PROM version                  |

| M37451E8DXXXSP |                     |                 |         | Extended operating temperature version |

| M37451E8SP     |                     |                 |         | One Time PROM version (blank)          |

| M37451M8-XXXFP |                     |                 |         | Mask ROM version                       |

| M37451M8DXXXFP |                     |                 |         | Extended operating temperature version |

| M37451E8-XXXFP | 16K                 | 384             | 80P6N-A | One Time PROM version                  |

| M37451E8DXXXFP |                     |                 |         | Extended operating temperature version |

| M37451E8FP     |                     |                 |         | One Time PROM version (blank)          |

| M37451M8-XXXGP |                     |                 |         | Mask ROM version                       |

| M37451E8-XXXGP |                     |                 | 80P6S-A | One Time PROM version                  |

| M37451E8GP     |                     |                 | ļ       | One Time PROM version (blank)          |

| M37451E8SS     |                     |                 | 64S1B   | EPROM version                          |

| M37451E8FS     | ,                   |                 | 80D0    | EPROM version                          |

| M37451MC-XXXSP |                     |                 | 64P4B   | Mask ROM version                       |

| M37451EC-XXXSP |                     |                 |         | One Time PROM version                  |

| M37451ECSP     |                     |                 |         | One Time PROM version (blank)          |

| M37451MC-XXXFP |                     |                 | 80P6N-A | Mask ROM version                       |

| M37451EC-XXXFP |                     |                 |         | One Time PROM version                  |

| M37451ECFP     | . 24K               | 512             |         | One Time PROM version (blank)          |

| M37451MC-XXXGP |                     |                 | 80P6S-A | Mask ROM version                       |

| M37451EC-XXXGP |                     |                 |         | One Time PROM version                  |

| M37451ECGP     |                     |                 |         | One Time PROM version (blank)          |

| M37451ECSS     |                     |                 | 64S1B   | EPROM version                          |

| M37451ECFS     |                     |                 | 80D0    | EPROM version                          |

| M37451SSP      |                     | 1024            | 64P4B   | External ROM version                   |

| M37451SFP      | ок                  |                 | 80P6N-A | External ROM version                   |

| M37451SGP      |                     |                 | 80P6S-A | External ROM version                   |

| M37451RSS      |                     |                 | 64S1M   | Emulator MCU                           |

| M37451RFS      |                     |                 | 80D0M   | Emulator MCU                           |

Use the EPROM version and the Emulator MCU for evaluation only. Do not use those for production applycations.

**■** 6249828 0024767 158 ■

# FUNCTIONAL DESCRIPTION Central Processing Unit (CPU)

The 7451 group uses the standard 740 family instruction set. Refer to the table of 740 family addressing modes and machine instructions or the SERIES 740 (Software) User's Manual for details on the instruction set.

Machine-resident 740 family instructions are as follows:

The FST and SLW instruction cannot be used.

The MUL, DIV, WIT, and STP instruction can be used.

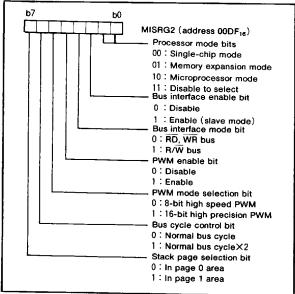

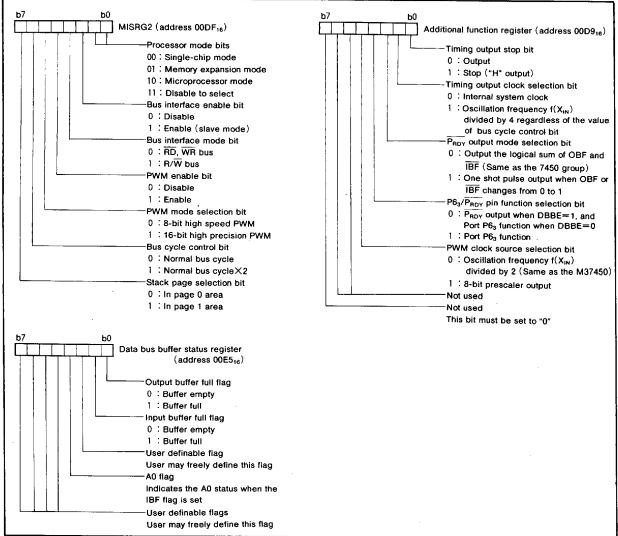

## **MISRG2 Register**

The MISRG2 register is allocated to address 00DF<sub>16</sub>. Bits 0 and 1 of this register are processor mode bits. This register also has a stack page selection bit.

. = 6249828 0024768 094 =

Fig. 1 Structure of MISRG 2

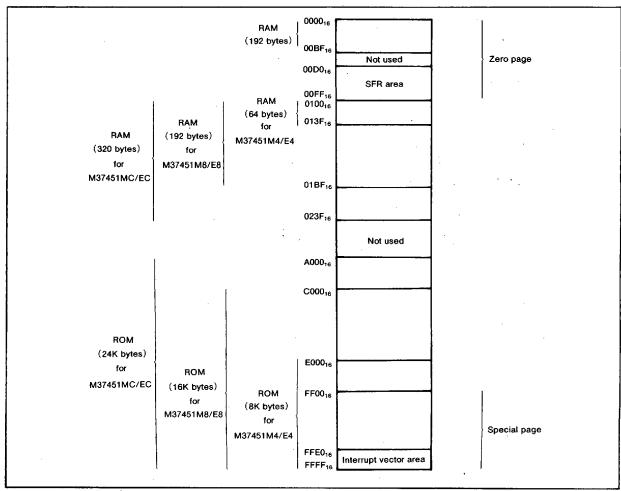

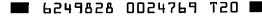

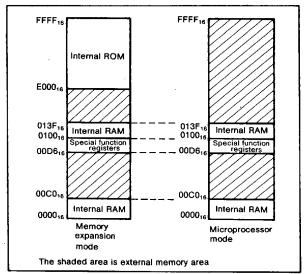

#### **MEMORY**

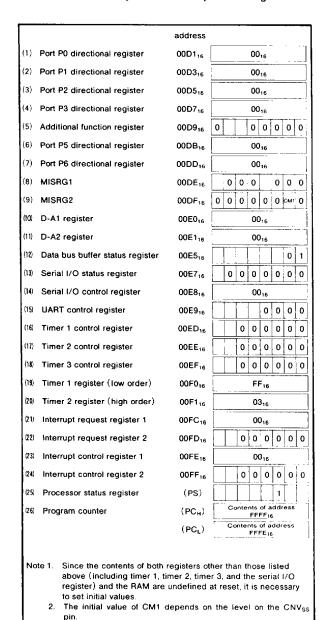

#### • Special Function Register (SFR) Area

The special function register area in the zero page contains control registers such as I/O ports and timers.

#### • BAM

RAM is used for data storage and for stack area of sub-routine calls and interrupts.

#### • ROM

ROM is used for storing user programs as well as the interrupt vector area.

#### • Interrupt Vector Area

The interrupt vector area is for storing jump destination addresses used at reset or when an interrupt is generated.

#### Zero Page

Zero page addressing mode is useful because it enables access to this area with only 2 bytes.

#### Special Page

Special page addressing mode is useful because it enables access to this area with only 2 bytes.

Fig. 2 Memory map (mask ROM version and PROM version)

Fig. 3 Memory map (external ROM version)

**■ 6249828 0024770 742 ■**

| 00D0 <sub>16</sub> | P0 register                      | 00EB <sub>16</sub> | PWM register (low-order)      |

|--------------------|----------------------------------|--------------------|-------------------------------|

| 00D1 <sub>16</sub> | P0 directional register          | 00EC <sub>16</sub> | PWM register (high-order)     |

| 00D2 <sub>16</sub> | P1 register                      | 00ED <sub>16</sub> | Timer 1 control register      |

| 00D3 <sub>16</sub> | P1 directional register          | 00EE <sub>16</sub> | Timer 2 control register      |

| 00D4 <sub>16</sub> | P2 register                      | 00EF <sub>16</sub> | Timer 3 control register      |

| 00D5 <sub>16</sub> | P2 directional register          | 00F0 <sub>16</sub> | Timer 1 register (low-order)  |

| 00D6 <sub>16</sub> | P3 register                      | 00F1 <sub>16</sub> | Timer 1 register (high-order) |

| 00D7 <sub>16</sub> | P3 directional register          | 00F2 <sub>16</sub> | Timer 1 latch (low-order)     |

| 00D8 <sub>16</sub> | P4 register/PWM prescaler latch  | 00F3 <sub>16</sub> | Timer 1 latch (high-order)    |

| 00D9 <sub>16</sub> | Additional function register     | 00F4 <sub>16</sub> | Timer 2 register (low-order)  |

| 00DA <sub>16</sub> | P5 register                      | 00F5 <sub>16</sub> | Timer 2 register (high-order) |

| 00DB <sub>16</sub> | P5 directional register          | 00F6 <sub>16</sub> | Timer 2 latch (low-order)     |

| 00DC <sub>16</sub> | P6 register                      | 00F7 <sub>16</sub> | Timer 2 latch (high-order)    |

| 00DD <sub>16</sub> | P6 directional register          | 00F8 <sub>16</sub> | Timer 3 register (low-order)  |

| 00DE <sub>16</sub> | MISRG1                           | 00F9 <sub>16</sub> | Timer 3 register (high-order) |

| 00DF <sub>16</sub> | MISRG2                           | 00FA <sub>16</sub> | Timer 3 latch (low-order)     |

| 00E016             | D-A1 register                    | 00FB <sub>16</sub> | Timer 3 latch (high-order)    |

| 00E1 <sub>16</sub> | D-A2 register                    | 00FC <sub>16</sub> | Interrupt request register 1  |

| 00E2 <sub>16</sub> | A-D register                     | 00FD <sub>16</sub> | Interrupt request register 2  |

| 00E3 <sub>16</sub> | A-D control register             | 00FE <sub>16</sub> | Interrupt control register 1  |

| 00E4 <sub>16</sub> | Data bus buffer register         | 00FF <sub>16</sub> | Interrupt control register 2  |

| 00E5 <sub>16</sub> | Data bus buffer status register  |                    |                               |

| 00E6 <sub>16</sub> | Receive/Transmit buffer register |                    | •                             |

| 00E7 <sub>16</sub> | Serial I/O status register       |                    |                               |

| 00E8 <sub>16</sub> | Serial I/O control register      |                    |                               |

| 00E9 <sub>16</sub> | UART control register            |                    |                               |

| 00EA16             | Baud rate generator              |                    |                               |

Fig. 4 SFR (Special Function Register) memory map (mask ROM version and PROM version)

| 00D6 <sub>16</sub> | P3 register                      | 00EB <sub>16</sub> | PWM register (low-order)      |

|--------------------|----------------------------------|--------------------|-------------------------------|

| 00D7 <sub>16</sub> | P3 directional register          | 00EC <sub>16</sub> | PWM register (high-order)     |

| 00D8 <sub>16</sub> | P4 register/PWM prescaler latch  | 00ED <sub>16</sub> | Timer 1 control register      |

| 00D9 <sub>16</sub> | Additional function register     | 00EE <sub>16</sub> | Timer 2 control register      |

| 00DA <sub>16</sub> | P5 register                      | 00EF <sub>16</sub> | Timer 3 control register      |

| 00DB <sub>16</sub> | P5 directional register          | 00F0 <sub>16</sub> | Timer 1 register (low-order)  |

| 10DC16             | P6 register                      | 00F1 <sub>16</sub> | Timer 1 register (high-order) |

| 0DD <sub>16</sub>  | P6 directional register          | 00F2 <sub>16</sub> | Timer 1 latch (low-order)     |

| 00DE <sub>16</sub> | MISRG1                           | 00F3 <sub>16</sub> | Timer 1 latch (high-order)    |

| 00DF <sub>16</sub> | MISRG2                           | 00F4 <sub>16</sub> | Timer 2 register (low-order)  |

| 0E0 <sub>16</sub>  | D-A1 register                    | 00F5 <sub>16</sub> | Timer 2 register (high-order) |

| 00E1 <sub>16</sub> | D-A2 register                    | 00F6 <sub>16</sub> | Timer 2 latch (low-order)     |

| 00E2 <sub>16</sub> | A-D register                     | 00F7 <sub>16</sub> | Timer 2 latch (high-order)    |

| 0E3 <sub>16</sub>  | A-D control register             | 00F8 <sub>16</sub> | Timer 3 register (low-order)  |

| 00E4 <sub>16</sub> | Data bus buffer register         | 00F9 <sub>16</sub> | Timer 3 register (high-order) |

| 00E5 <sub>16</sub> | Data bus buffer status register  | 00FA <sub>16</sub> | Timer 3 latch (low-order)     |

| 00E6 <sub>16</sub> | Receive/transmit buffer register | 00FB <sub>16</sub> | Timer 3 latch (high-order)    |

| 00E7 <sub>16</sub> | Serial I/O status register       | 00FC <sub>16</sub> | Interrupt request register 1  |

| 00E8 <sub>16</sub> | Serial I/O control register      | 00FD <sub>16</sub> | Interrupt request register 2  |

| 00E9 <sub>16</sub> | UART control register            | 00FE <sub>16</sub> | Interrupt control register 1  |

| 00EA <sub>16</sub> | Baud rate generator              | 00FF <sub>16</sub> | Interrupt control register 2  |

Fig. 5 SFR (Special Function Register) memory map (external ROM version)

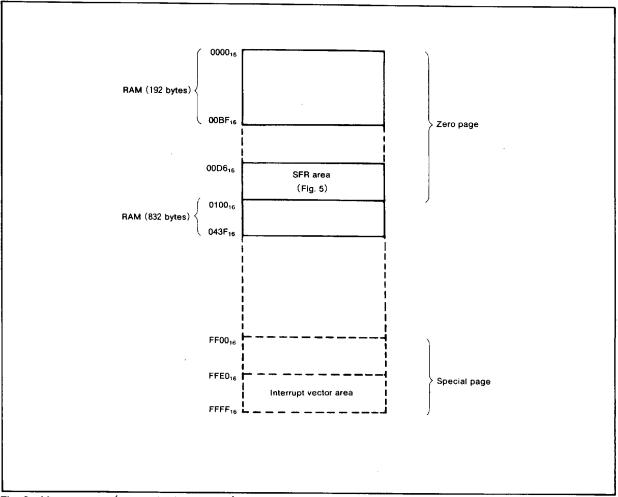

#### INTERRUPTS

Interrupts can be caused by 15 different events consisting of six external, eight internal, and one software events.

Interrupts are vectored interrupts with priorities shown in Table 1. Reset is also included in the table because its operation is similar to an interrupt.

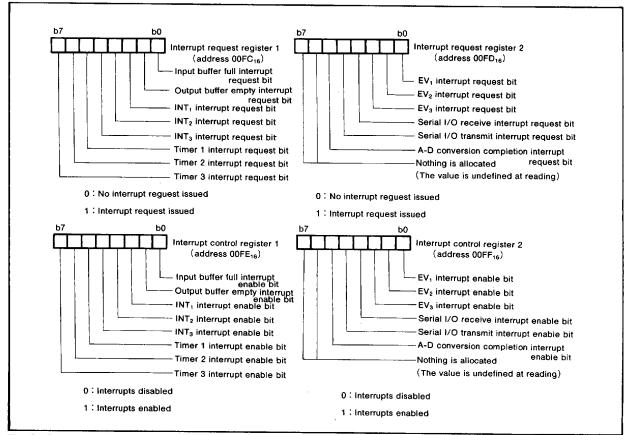

When an interrupt is accepted, the registers are pushed, interrupt disable flag I is set to "1", and the program jumps to the address specified in the vector table. The interrupt request bit is cleared automatically. The reset and BRK instruction interrupt can never be disabled. Other interrupts are disabled when the interrupt disable flag is set to "1".

All interrupts except the BRK instruction interrupt have an interrupt request bit and an interrupt enable bit. The interrupt request bits are in interrupt request registers 1 and 2 and the interrupt enable bits are in interrupt control registers 1 and 2. Figure 6 shows the structure of the interrupt request registers 1 and 2 and interrupt control registers 1 and 2.

Interrupts other than the BRK instruction interrupt and reset are accepted when the interrupt enable bit is "1", interrupt request bit is "1", and the interrupt disable flag is "0". The interrupt request bit can be reset with a program, but not set. The interrupt enable bit can be set and reset with a program.

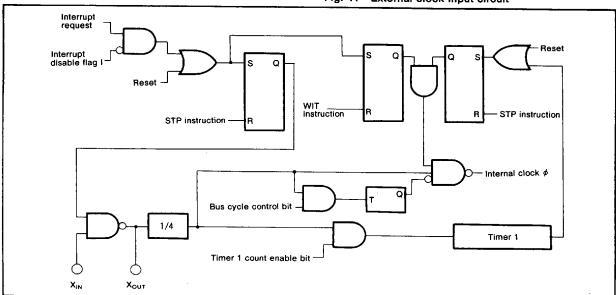

Reset is treated as a non-maskable interrupt with the highest priority. Figure 7 shows interrupts control.

Table 1. Interrupt vector address and priority.

| Event                               | Priority | Interrupt vector addresses              | Remarks                                          |

|-------------------------------------|----------|-----------------------------------------|--------------------------------------------------|

| RESET                               | 1        | FFFF <sub>18</sub> , FFFE <sub>16</sub> | Non-maskable                                     |

| Input buffer full interrupt         | 2        | FFFD <sub>16</sub> , FFFC <sub>16</sub> | Valid only in slave mode                         |

| Output buffer empty interrupt       | 3        | FFFB <sub>16</sub> , FFFA <sub>16</sub> | Valid only in slave mode                         |

| INT <sub>1</sub> interrupt          | 4        | FFF9 <sub>16</sub> , FFF8 <sub>16</sub> | External interrupt (polarity programmable)       |

| INT <sub>2</sub> interrupt          | 5        | FFF7 <sub>16</sub> , FFF6 <sub>18</sub> | External interrupt (polarity programmable)       |

| INT <sub>3</sub> interrupt          | 6        | FFF5 <sub>16</sub> , FFF4 <sub>16</sub> | External interrupt (polarity programmable)       |

| Timer 1 interrupt                   | 7        | FFF3 <sub>16</sub> , FFF2 <sub>16</sub> |                                                  |

| Timer 2 interrupt                   | 8        | FFF1 <sub>16</sub> , FFF0 <sub>16</sub> |                                                  |

| Timer 3 interrupt                   | 9        | FFEF <sub>16</sub> , FFEE <sub>16</sub> |                                                  |

| EV <sub>1</sub> interrupt           | 10       | FFED <sub>18</sub> , FFEC <sub>16</sub> | External event interrupt (polarity programmable) |

| EV <sub>2</sub> interrupt           | 11       | FFEB <sub>16</sub> , FFEA <sub>16</sub> | External event interrupt (polarity programmable) |

| EV <sub>3</sub> interrupt           | 12       | FFE9 <sub>16</sub> , FFE8 <sub>16</sub> | External event interrupt (polarity programmable) |

| Serial I/O receive interrupt        | 13       | FFE7 <sub>16</sub> , FFE6 <sub>16</sub> | Valid only when serial I/O is selected           |

| Serial I/O transmit interrupt       | 14       | FFE5 <sub>16</sub> , FFE4 <sub>16</sub> | Valid only when serial I/O is selected           |

| A-D conversion completion interrupt | 15       | FFE3 <sub>16</sub> , FFE2 <sub>16</sub> |                                                  |

| BRK instruction interrupt           | 16       | FFE1 <sub>16</sub> , FFE0 <sub>16</sub> | Non-maskable software interrupt                  |

Fig. 6 Structure of registers related to interrupt

Fig. 7 Interrupt control

**■** 6249828 0024774 398 **■**

#### TIMER

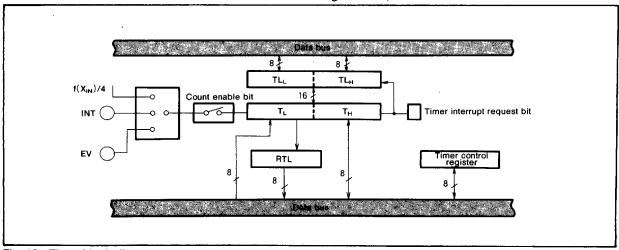

The 7451 group has three independent 16-bit internal timers as shown in Figure 10.

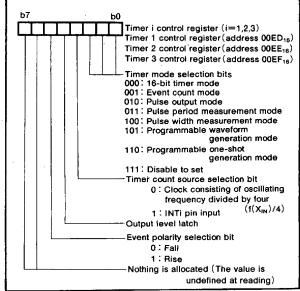

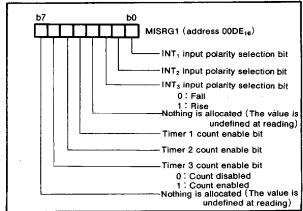

The timers are controlled by the timer i control register (i= 1, 2, 3) and MISRG1 shown in Figure 8 and 9.

The timer and the timer latch are independent of each other and a value must be written in both when setting a timer.

A write to a timer is performed in the order of  $T_L$  to  $T_H$  after setting the count enable bit to count inhibit "0".

A read from a timer is performed in the order of  $T_H$  to  $T_L$ . The value of  $T_L$  is latched in the read timer latch at the timing when  $T_H$  is read. All timers are decrement counters and are started by setting the timer i count enable bit to "1". When the value of the timer reaches  $0000_{16}$ , and overflow occurs and the timer i interrupt request bit is set to "1" at the next count pulse.

During a reset or an STP instruction execution, the low-order byte of the timer 1 register is set to  $FF_{16}$  and the high-order byte is set to  $03_{16}$ . Also, when an STP instruction is executed, a clock obtained by dividing the oscillating frequency by four  $(f(X_{IN})/4)$  becomes the timer 1 count source regardless of the timer 1 count source selection bit. This condition is canceled and the original count source is resumed when the timer i interrupt request bit is set to "1" or when a reset occurs. Refer to the section on the clock generator for details concerning the operation of the STP instruction.

The 7451 group provides seven timer modes selectable with the timer mode selection bit in the timer i control register.

Fig. 8 Structure of timer i control register

Fig. 9 Structure of MISRG1

Fig. 10 Timer block diagram

**-** 6249828 0024775 224 **-**

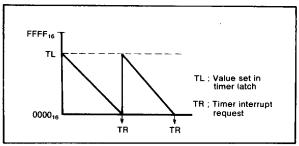

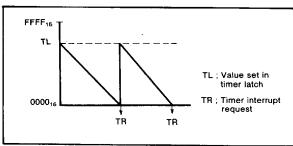

## (1) 16-bit Timer Mode [000]

In this mode, an interrupt request occurs and the value of the timer latch is loaded in the timer each time the timer overflows.

The timer count source is set to  $f(X_{1N})$  divided by four regardless of the count sorce selection bit. Assuming that the timer latch is n, the frequency dividing ratio is 1/(n+1).

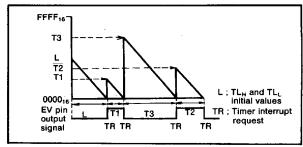

Figure 11 shows the timer operation during 16-bit timer mode.

Fig. 11 16-bit timer mode operation

## (2) Event Count Mode [001]

In this mode, the EVi pin input signal are counted in the direction selected by the event input polarity selection bit.

The input signal from the EVi pin is used as the count source regardless of the timer count source selection bit. The operation is the same as with the 16-bit timer mode except for the difference in the count source.

Both the "H" and "L" pulse width of the EVi pin input signal must be not less than  $(4/f(X_{\rm IN}))+100{\rm ns}$ .

Figure 12 shows the timer operation during event count mode.

Fig. 12 Event counter mode operation

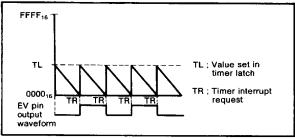

## (3) Pulse Output Mode [010]

In this mode, a 50% duty pulse is output from the EVi pin. The count source selected with the timer count source selection bit is counted. When it overflows, the phase of the EVi pin output level is reversed and the value of the timer latch is loaded in the timer.

When this mode is selected, the EVi pin output level is initialized to "L".

Figure 13 shows the timer operation during pulse output mode.

Fig. 13 Pulse output mode

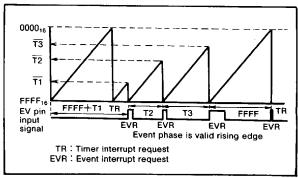

# (4) Pulse Period Measurement Mode [011]

This mode is used to measure the pulse period of the EVi pin input signal.

The timer counts the count source selected by the count source selection bit between the rise-to-rise or fall-to-fall interval (selected with the event input polarity selection bit in the timer i control register) of the EVi pin input signal.

At a valid edge on the EVi pin input, the 1's complement of the timer value is stored in the timer latch and the timer value is set to  $\mathsf{FFFF}_{16}$ .

Figure 14 shows the timer operation during pulse frequency measurement mode.

Fig. 14 Pulse period measurement mode

**■** 6249828 0024776 160 **■**

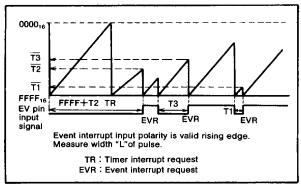

## (5) Pulse Width Measurement Mode [100]

This mode measures the pulse width while the EVi pin input signal is "H" or "L".

Whether to measure the "H" or "L" interval is determined by the event input polarity selection bit. If this bit is "0", the count source selected with the count source selection bit is counted while the input pulse is "H". If it is "1", the count source is counted while the input pulse is "L". A 1's complement of the timer value is stored in the timer latch for a valid edge on the EVi pin input. In addition, the timer value is set to FFFF<sub>16</sub> for an edge (both rise and fall) on the EVi pin input. Figure 15 shows the timer operation during pulse width measurement mode.

Fig. 15 Pulse width measurement mode

In pulse period measurement mode [011] and pulse width measurement mode [100], an EVi interrupt request is issued at the valid edge selected by the event phase selection bit. That is, an interrupt occurs at the end of the pulse period measurement or pulse width measurement. Also, when a timer overflow occurs, the count continues from FFFF<sub>16</sub> without the value of the timer latch being loaded in the timer.

Write to timer latch is inhibited in pulse period measurement mode and pulse width measurement mode. Furthermore, EVi interrupt is disabled during STP instruction execution.

# (6) Programmable Waveform Generation Mode [101]

In this mode, the level set in the output level latch of the timer i control register is output to the EVI pin every time the timer overflows.

The timer counts the source selected by the count source selection bit and when it overflows, the value in the timer latch is loaded in the timer.

After it overflows, the value of the output level latch and the timer latch can be modified to generate any waveform from the EVi pin.

Figure 16 shows the timer operation during programmable waveform generation mode.

Fig. 16 Programmable waveform generation mode

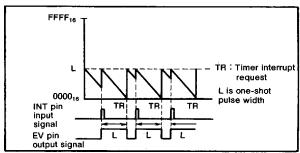

# (7) Programmable One-shot Generation Mode [110]

This mode uses the INTi pin input signal as a trigger and counts by writing the value of the timer latch in the timer.

The output level of the EVi pin goes "H" when the trigger is issued and goes "L" when the timer overflows.

The EVi pin level is initialized to "L" when this mode is selected.

The timer count source is set to  $f(X_{\text{IN}})$  divided by four regardless of the count source selection bit.

A valid edge of the INTi pin input trigger signal is determined by the INTi phase selection bit of MISRG1 (00DE<sub>16</sub>). Figure 17 shows the timer operation during programmable one-shot generation mode.

Fig. 17 Programmable one-shot generation mode

When the INTi pin input signal is selected as the count source for pulse output mode [010], pulse period measurement mode [011], pulse width measurement mode [100], and programmable waveform generation mode [101], the "H" and "L" pulse width of the input signal must not be less than  $(6/f(X_{IN}))+100$ ns.

6249828 0024777 OT7 |

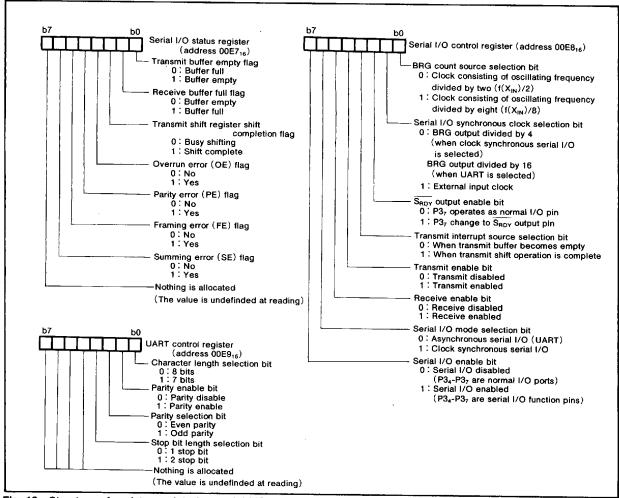

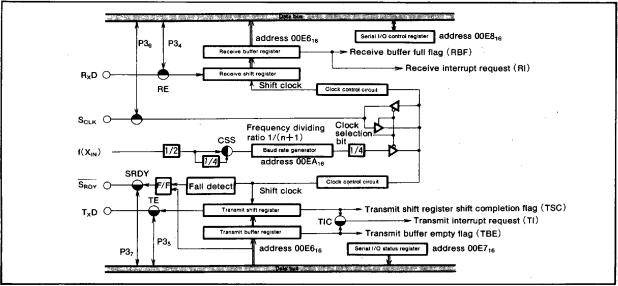

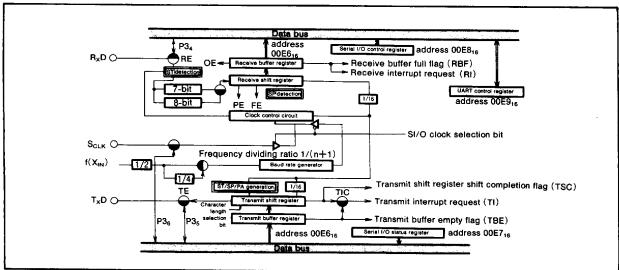

#### SERIAL I/O

Serial I/O can operate in either clock synchronous or clock asynchronous (UART) mode. An exclusive baud rate gen-

eration timer (baud rate generator) is provided for serial I/O operation. Figure 18 shows the structure of the registers used for serial I/O.

Fig. 18 Structure of registers related to serial I/O

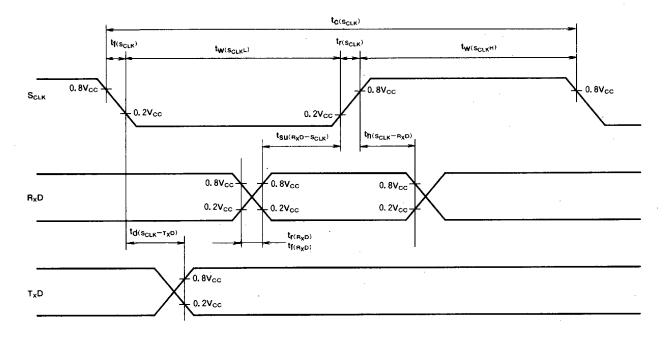

## (1) Clock Synchronous Serial I/O

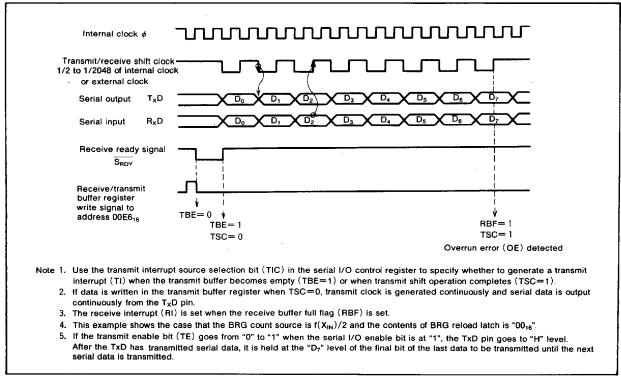

Clock synchronous serial I/O is selected by setting the mode selection bit of the serial I/O control register to "1". Figure 19 shows a block diagram of clock synchronous serial I/O and Figure 20 shows its operation.

With clock synchronous serial I/O, the same clock is used as the operating clock between the transmitting and receiving microcomputers. If an internal clock is used for operating clock, transmit/receive is started by writing a signal in the transmit/receive buffer register.

Fig. 19 Clock synchronous serial I/O block diagram

Fig. 20 Clock synchronous serial I/O operation

**■** 6249828 0024779 97T **■**

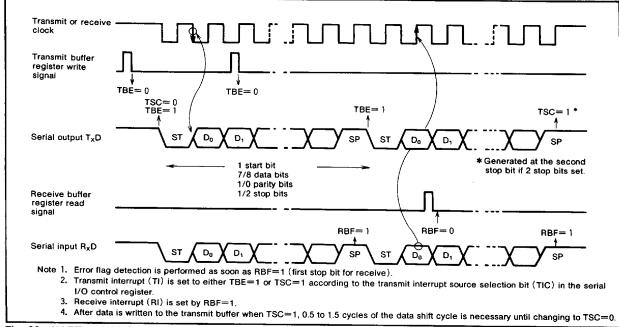

## (2) Clock Asynchronous Serial I/O (UART)

UART is selected by setting the mode selection bit of the serial I/O control register to "0". Figure 21 shows a block diagram of UART and Figure 22 shows its operation.

With the 7451 group, one of eight serial data transmission formats can be selected with the UART control register as shown in Figure 18. The transmission format must be agreed upon between the transmit side and the receive side.

The transmit shift register and the receive shift register has its buffer register respectively to perform serial data transfer (same memory addresses).

Data cannot be written or read directly to/from the shift registers. Therefore, the data to be transmitted is written to a buffer register and the received data is read from a buffer register. The buffer registers can also be used to store data to be transmitted next or to receive 2-byte data consecutively.

Fig. 21 UART serial I/O block diagram

Fig. 22 UART serial I/O operation

**■** 6249828 0024780 691

2-29

## [Serial I/O control register] SIOCON

The serial I/O control register is an 8-bit register consisting of selection bits for controlling the serial I/O function.

#### · Serial I/O enable bit SIOE

When this bit is set to "1", serial I/O is enabled and pins  $P3_4-P3_7$  can be used as serial I/O function pins.

#### · Serial I/O mode selection bit SIOM

This bit is used to select the serial I/O operation mode. When this bit is "0", asynchronous serial I/O (UART), which transfers data using start and stop bits, is selected. When it is "1", clock synchronous serial I/O which performs transmission and receive using the same clock is selected.

#### · Receive enable bit RE

Receive operation is enabled when this bit is set to "1" and pin P3<sub>4</sub> becomes a serial data input pin.

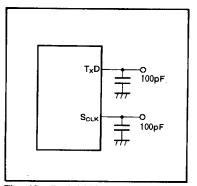

#### · Transmission enable bit TE

Transmission operation is enabled when this bit is set to "1". Pin P3<sub>5</sub> becomes a serial data output pin and shift data is output.

#### · Transmission interrupt source selection bit TIC

This bit is used to select events that can cause a transmission interrupt.

#### · Spry output enable bit SRDY

If this bit is set to "1" when clock synchronous serial I/O is selected, pin P3 $_7$  becomes an  $\overline{S_{RDY}}$  signal output pin and  $\overline{S_{RDY}}$  signal is output.

When an external clock is used during clock synchronous serial I/O, the  $\overline{S_{RDY}}$  signal is used to notify the clock sender that it can send the serial clock signal. It goes "L" when data is written in the transmit/receive buffer register and goes "H" at the first fall of the receive clock. When using the  $\overline{S_{RDY}}$  signal, the transmission enable bit must be set to "1" even when performing receive only.

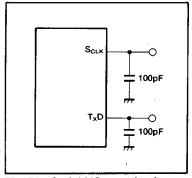

### · Serial I/O synchronous clock selection bit SCS

When this bit is "1", pin  $P3_6$  becomes an input pin and the external clock input from the  $S_{CLK}$  pin is selected as the serial I/O synchronous clock. When this bit is "0", the baud rate generator (BRG) overflow signal is selected as the serial I/O synchronous clock. Also, when this bit is "0" during clock synchronous serial I/O, pin  $P3_6$  becomes an output pin and the shift clock is output from the  $S_{CLK}$  pin.

When clock synchronous serial I/O is selected, the baud rate generator (BRG) output signal divided by four or an external clock input is used. When UART is selected, the BRG output signal divided by sixteen or an external clock input signal divided by sixteen is used.

#### · BRG count source selection bit CSS

The baud rate generator is an 8-bit counter with a reload register. By setting a value n in the BRG register (address 00EA<sub>16</sub>), the count source selected by the BRG count source selection bit is divided by (n+1).

## [UART control register] UARTCON

The UART control register is a 4-bit register consisting of control bits that are valid when UART is selected. The content of this register is used to set the data format for serial data transmission/receiving.

#### · Character length selection bit CHAS

This bit is used to select the transmission/receiving character length.

#### · Parity enable bit PARE

When this bit is set to "1", a parity bit is added next to the most significant bit (MSB) of the transmission data and parity is checked during receive.

#### · Parity selection bit PARS

This bit is used to specify the type of parity to be generated during transmission and checked when data is received. The number of 1's in the data is set to even or odd according to this bit.

#### Stop bit length selection STPS

This bit is used to determine the number of stop bits to be used during transmission.

## [Serial I/O status register] SIOSTS

The serial I/O status register is a 7-bit read only register consisting of serial I/O operation status flags and error flags. Bits 4 to 6 are valid only during UART mode.

All bits of this register are initialized to "0" at reset, and when the transmit enable bit in the serial I/O control register is set to "1", bits "0" and "2" change to "1".

## Transmission buffer empty flag TBE

This bit is cleared to "0" when transmission data is written in the transmission buffer register and set to "1" when that data is transferred to the transmit shift register. It is also cleared when TE=0.

#### · Receive buffer full flag RBF

When receiving serial data, data is transferred to the receive buffer register and this bit is set to "1" when the receive shift register completes receiving a data byte. This bit is cleared when the data is read. This bit is also cleared when RE=0.

#### · Transmit shift register shift completion flag TSC

This bit is cleared to "0" when the data in the transmission buffer register is transferred to the transmit shift register and set to "1" when data shift completes. It is also set to "1" when TE=0.

#### · Overrun error flag OE

When continuously receiving serial data, this bit is set when the next data fill the receive shift register before the data in the receive buffer register has been read.

#### · Parity error flag PE

When receiving serial data with parity, this bit is set to "1" if the parity of the received data differs from the specified parity.

6249828 002478<u>1</u> 528 **1**

#### · Framing error flag FE

This bit is set to "1" when there is no stop bit when transferring data from the receive shift register to the receive buffer.

#### · Summing error flag SE

This bit is set when either overrun, a parity, or a framing error occurs.

Tests for these errors are performed as soon as the data is transferred from the receive shift register to the receive buffer register and at the same time the receive buffer full flag is set. The error flags (OE, PE, FE, and SE) are cleared when any data is written in the serial I/O status register. Also, all status flags including error flags are cleared when SIOE=0.

#### **Usage cautions**

(1) To reset the serial I/O control register

Reset the serial I/O control register after disabling the transmit and receive enable bits that were enabled at that point and resetting the transmit and receive circuits. If the serial I/O control register is reset without resetting the other items, the settings will not operate correctly.

(2) Transmit and receive interrupt requests when transmit and receive enable bits are set.

Setting the transmit and receive enable bits to "1" sets the receive buffer empty flag and the transmit shift register shift completion flag to "1". Therefore, an interrupt request is generated and the transmit interrupt request bit is set, regardless of which timing is selected for the generation of transmit interrupts.

If interrupts of this timing are not used, first clear the transmit interrupt enable bit to "0" (disabled status), set the transmit enable bit, then clear the transmit interrupt request bit again after executing one instruction (e. g., the NOP instruction). Finally, set the transmit interrupt enable bit to "1" (enabled status).

(3) To disable transmission after one byte of data has been transmitted.

The method used in the M37451 to post the completion of data transmission is to reference the transmit shift register shift completion flag (TSC flag). The TSC flag is cleared to "0" while data is being transmitted, and it is set to "1" when the data transmission is completed. Therefore, if transmission is disabled after it has been confirmed that the TSC flag has been set, transmission can be forced to end after one byte of data is transmitted.

However, the TSC flag can also be set by enabling serial I/O, but it is not cleared by shift clock generation and transmission start (after data has been transferred from the transmit buffer to the transmit shift register, af-

ter 0.5 to 1.5 cycles of the shift clock), so if the TSC flag is referenced and transmission is disabled at this point, data will not be transmitted. Make sure that the TSC flag is referenced after transmission has started.

**■** 6249828 0024782 464 ■

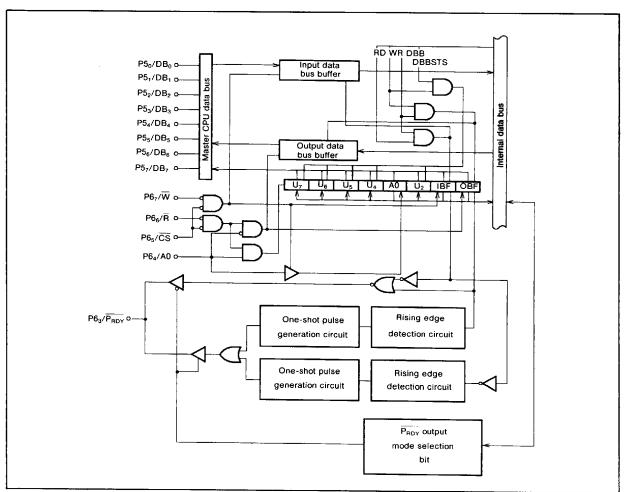

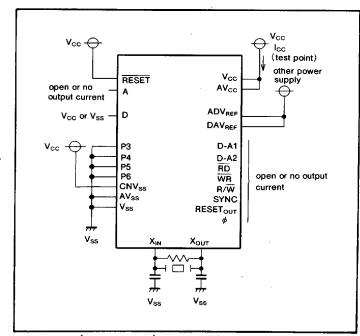

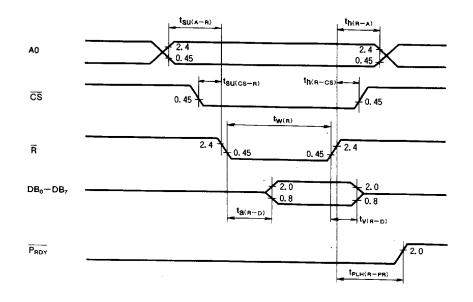

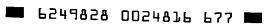

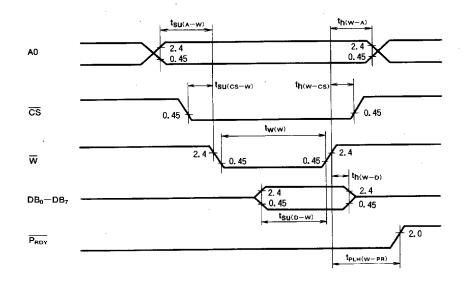

## **BUS INTERFACE**

The 7451 group is equipped with a bus interface that is functionally similar to the MELPS 8-41 series. Its operation can be controlled with control signals from the host CPU (slave mode).

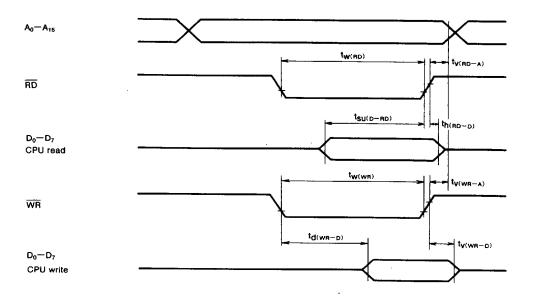

The 7451 group bus interface can be connected directly to either a R/ $\overline{W}$  type CPU or separate  $\overline{RD}$ ,  $\overline{WR}$  type CPU. Figure 23 shows a block diagram of the bus interface function. Slave mode is selected with MISRG2 (address 00DF<sub>16</sub>) bit 2 and 3 as shown in Figure 24.

An input buffer full interrupt occurs when data is received from the host CPU and an output buffer empty interrupt occurs when data is read by the host CPU.

In slave mode, ports  $P5_0-P5_7$  become a tri-state data bus used to transfer data, commands, and status to and from the host CPU.

Furthermore, ports P6<sub>4</sub>-P6<sub>7</sub> become host CPU control signal input pins and P6<sub>3</sub> becomes a slave status output pin.

Fig. 23 Bus Interface circuit diagram

Fig. 24 Structure of bus interface relation registers

## [Data bus buffer status register] DBBSTS

This is an 8-bit register. Bits 0, 1, and 3 are read-only bits indicating the status of the data bus buffer. Bits 2, 4, 5, 6, and 7 are read/write enabled user-definable flags that can be set with a program. The host CPU can only read these flags by setting the A0 pin to "H".

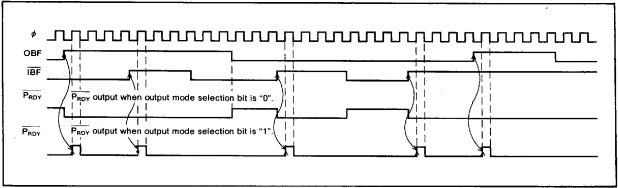

#### · Output buffer full flag OBF

This flag is set when data is written in the output data bus buffer and cleared when the host CPU reads the data in the output data bus buffer. When the  $\overline{P_{RDY}}$  output mode selection bit is "0", OBF is initialized to "1" only at reset and is cleared to "0" by setting the bus interface enable bit to "1". In this case, OBF is set to "1" when the bus interface enable bit changes from "1" (enable) to "0" (disable). But when the bus interface enable bit is set to "1" again, it is set to the value directly before clearing the bus interface enable bit. When the  $\overline{P_{RDY}}$  output mode selection bit is "1", OBF is initialized to "1" when the bus interface enable bit is cleared to "0" or reset.

In this case, OBF is set to "1" by clearing the bus interface enable bit and it is cleared to "0" by setting the bus interface enable bit.

#### · Input buffer full flag IBF

This flag is set when the host CPU writes data in the input

data bus buffer and cleared when the slave CPU reads the data in the input data bus buffer. When the  $\overline{P_{RDY}}$  output mode selection bit is "0", IBF is initialized to "0" only at reset.

When the  $\overline{P_{RDY}}$  output mode selection bit is "1", IBF is initialized to "0" when the bus interface enable bit is cleared to "0" or reset.

## A0 Flag

The level of the A0 pin is latched when the host CPU writes data in the input data bus buffer.

## [Input data bus buffer] DBBIN

Data on the data bus is latched in DBBIN when there is a write request from the host CPU. The data in DBBIN can be read from the data bus buffer register (SFR address 00E4<sub>16</sub>).

## [Output data bus buffer] DBBOUT

Data is written in DBBOUT by writing data in data bus buffer register (SFR address 00E4<sub>16</sub>). The data in DBBOUT is output to the data bus (P5) when the host CPU issues a read request with setting the A0 pin to "L".

Table 2. Control I/O pin functions when bus interface function is selected

| Pin               | Name             | Bus interface<br>mode bit |   | P6 <sub>3</sub> /P <sub>RDY</sub> pin<br>function selection bit | input/<br>Output | Function                                                                                                                                                                                                                             |

|-------------------|------------------|---------------------------|---|-----------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| P6 <sub>3</sub>   | P <sub>RDY</sub> | _                         | 0 | 0                                                               | Output           | Status output. The NOR of OBF and IBF is output.                                                                                                                                                                                     |

| 1                 |                  |                           |   | 1                                                               | 1/0              | Port P6 <sub>3</sub> function.                                                                                                                                                                                                       |

|                   |                  |                           | 1 | 0                                                               | Output           | Status output. Normally output "0".  One shot pulse whose length is half of a period of Internal system clock $\phi$ is output, when OBF or $\overline{\text{IBF}}$ changes from "0" to "1".  (Refer to Figure. 25)                  |

|                   |                  |                           |   | 1                                                               | 1/0              | Port P6 <sub>3</sub> function.                                                                                                                                                                                                       |

| P6 <sub>4</sub>   | AO               | _                         | _ | _                                                               | Input            | Address input. Used to select between DBBSTS and DBBOUT during host CPU read. Also used to identify commands and data during write.                                                                                                  |

| P6 <sub>5</sub> . | cs               |                           |   | _ [                                                             | Input            | Chip select input. Used to select the data bus buffer. Select when "L".                                                                                                                                                              |

| P6 <sub>6</sub>   | R                | 0                         | _ | _                                                               | Input            | Timing signal used by the host CPU to read data from the data bus buffer.                                                                                                                                                            |

|                   | E                | 1                         | - |                                                                 | Input            | Inputs a timing signal E or inverse of $\phi$ .                                                                                                                                                                                      |

| P6 <sub>7</sub>   | w                | 0                         | _ | _                                                               | Input            | Timing signal used by the host CPU to write data to the data bus buffer.                                                                                                                                                             |

|                   | R/W              | 1                         | _ |                                                                 | Input            | Input $R/\overline{W}$ signal used to control the data transfer direction. When this signal is "L", data bus buffer write is synchronized with the E signal. When it is "H", data bus buffer read is synchronized with the E signal. |

Fig. 25 Output status of PRDY pin

■ 6249828 0024786 00T ■

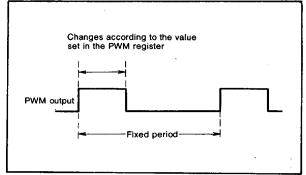

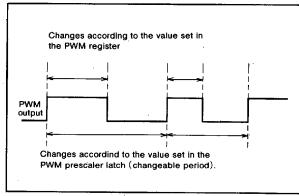

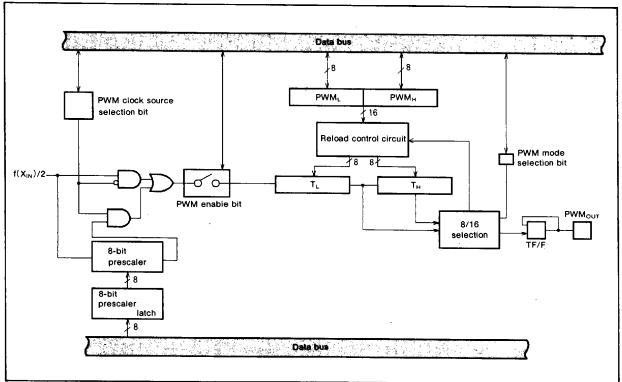

#### **PWM**

The PWM generator has two program-selectable modes; the high-speed mode (8-bit resolution) and the high-precision mode (16-bit resolution).

Also two clocks listed below can be selected as the count clock of each PWM mode.

- Oscillation frequency f(X<sub>IN</sub>) divided by 2

- 8-bit prescaler output (The count source of prescaler is oscillation frequency f(X<sub>IN</sub>) divided by 2)

Figure 28 shows a block diagram of PWM.

The count clock of PWM can be selected by the PWM clock source selection bit of additional function register (address 00D9<sub>16</sub>). And the register MISRG2 (address 00DF<sub>16</sub>) is used to enable/disable the PWM and change its mode. When the PWM enable bit is set, the PWM generator starts from its initial state.

When PWM clock source selection bit is "0", as shown in Figure 26, the output period is fixed.

In high-speed mode

$(2\times255)/f(X_{IN})$  40.8 $\mu$ s at  $f(X_{IN})=12.5MHz$ In high-precision mode